# NY8LP05A

# 8-bit 65C02 MCU with 4x15 LCD Driver, 16 I/O, & Buzzer Output

## Version 1.1

Nov. 30, 2020

ChipSourceTek Technology Co. reserves the right to change this document without prior notice. Information provided by ChipSourceTek is believed to be accurate and reliable. However, ChipSourceTek makes no warranty for any errors which may appear in this document. Contact ChipSourceTek to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by ChipSourceTek for any infringement of patent or other rights of third parties which may result from its use. In addition, ChipSourceTek products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of ChipSourceTek.

ShenZhen ChipSourceTek Technology Co. , Ltd.

# **Revision History**

# NY8LP05A

| Version | Date       | Description                                                                                                                                                                                                                                                                                                                                             | Modified Page                           |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 0.3     | 2020/06/01 | Preliminary Edition                                                                                                                                                                                                                                                                                                                                     | -                                       |

| 1.0     | 2020/08/31 | <ol> <li>Feature list updated.</li> <li>Section 5.1 8MHz -&gt; 4MHz.</li> <li>Section 6.1 Timer2/Timer1/Timer0 -&gt; Timer1/Timer0.</li> <li>Section 8.2 LCD RAM table updated.</li> <li>Section 12.2 F<sub>CPU</sub> = 32KHz -&gt; 500KHz.</li> <li>Section 13.1 Diode in keyscan diagram removed.</li> <li>Section 14 PAD diagram updated.</li> </ol> | 5,7<br>10<br>16<br>26<br>41<br>43<br>45 |

| 1.1     | 2020/11/30 | <ol> <li>Add Note "It needs to be cautious to use OPMD to divide the clock frequency. Please refer to AP-Note 34 for details." at Section 5.2.</li> <li>Modify the Die Pad Diagram.</li> </ol>                                                                                                                                                          |                                         |

CC

# NY8LP05A

# **Table of Contents**

| 1. | 概述  | <u>}</u>                                       | 5  |

|----|-----|------------------------------------------------|----|

| 2. | 功能  | <u>.</u>                                       | 5  |

| 1. | GEN | NERAL DESCRIPTION                              | 7  |

| 2. | FEA | ATURES                                         | 7  |

| 3. | BLO | OCK DIAGRAM                                    | 8  |

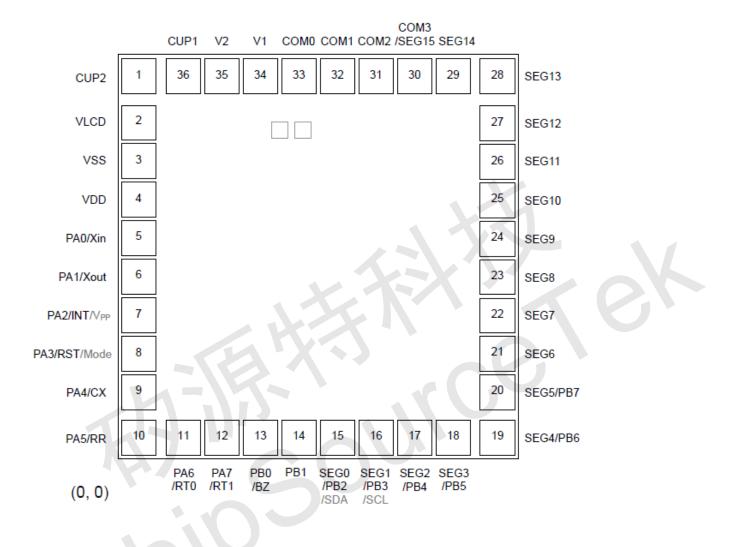

| 4. |     | D DESCRIPTION                                  |    |

| 5. | Оре | eration Modes                                  | 10 |

|    | 5.1 | Clock Source                                   | 10 |

|    | 5.2 | Normal Mode                                    |    |

|    | 5.3 |                                                | 13 |

|    | 5.4 | Standby Mode                                   | 13 |

|    | 5.5 | Halt mode                                      |    |

| 6. |     | tem Control                                    |    |

|    | 6.1 | Reset System                                   | 15 |

|    |     | 6.1.1 Power-On Reset (POR)                     |    |

|    |     | 6.1.2 Low Voltage Reset (LVR)                  | 15 |

|    |     | 6.1.3 External Reset Pin (by option)           | 15 |

|    |     | 6.1.4 Watch-Dog Timer Reset (WDTR) (by option) | 15 |

|    |     | 6.1.5 Low Voltage Detector (LVD)               |    |

|    | 6.2 | Interrupts                                     |    |

| 7. | Add | Iress Mapping                                  | 20 |

|    | 7.1 | Control Register Description                   |    |

|    | 7.2 | RAM                                            | 24 |

|    | 7.3 | ROM                                            | 24 |

| 8. | LCD | ) Control                                      | 25 |

ShenZhen ChipSourceTek Technology Co. , Ltd.

|      | 8.1   | LCD Power Supply                                                                                                                     | NY8LP05A |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

|      |       | 8.1.1 Power Pumping Mode                                                                                                             |          |

|      | 8.2   | LCD RAM Alignment                                                                                                                    |          |

|      | 8.3   | LCD Display System                                                                                                                   | 27       |

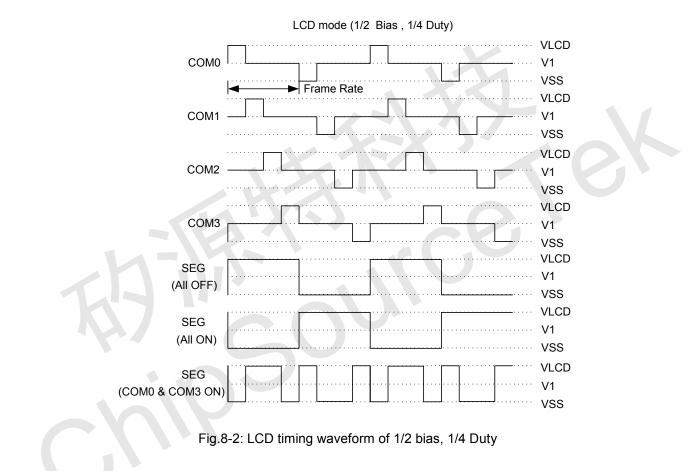

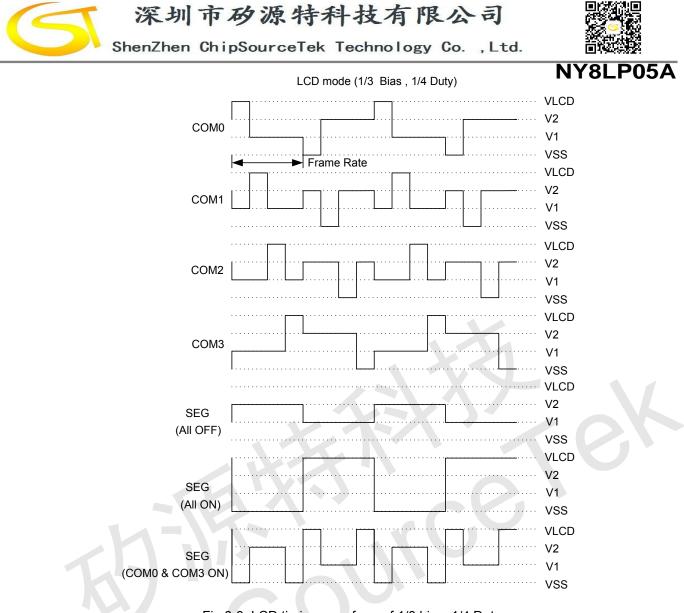

|      | 8.4   | LCD WAVEFORMS                                                                                                                        | 29       |

| 9. E | Buzze | er                                                                                                                                   | 31       |

|      | 9.1   | Buzzer Control                                                                                                                       |          |

|      | 9.2   | TMxD(x=0,1,2)                                                                                                                        |          |

|      | 9.3   | TMxC(x=0,1,2)                                                                                                                        |          |

|      | 9.4   | TMxEN(x=0,1,2)                                                                                                                       |          |

| 10.  | I/O   | Control                                                                                                                              | 34       |

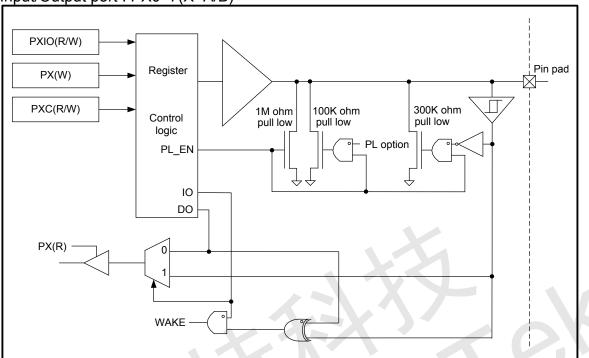

|      |       | I/O Ports                                                                                                                            |          |

| 11.  | Othe  | er Applications (by option)                                                                                                          | 36       |

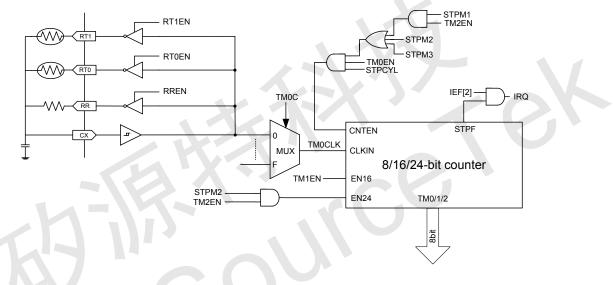

|      | 11.1  | Resistor to Frequency Converter (RFC)                                                                                                |          |

|      |       | 11.1.1 RC Oscillation Network                                                                                                        |          |

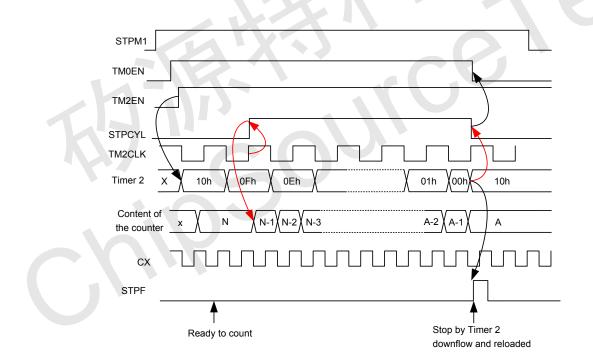

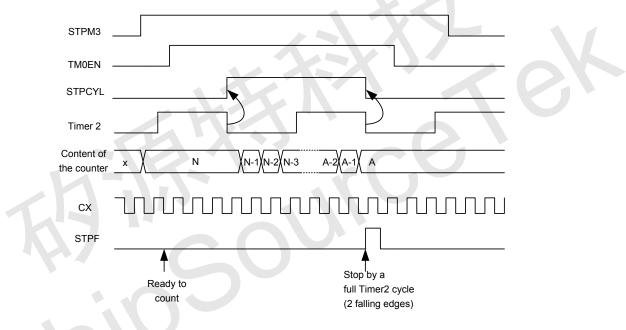

|      |       | 11.1.2 Timer0 Counting within Timer2 Overflow Cycle (STOP Mode1)                                                                     |          |

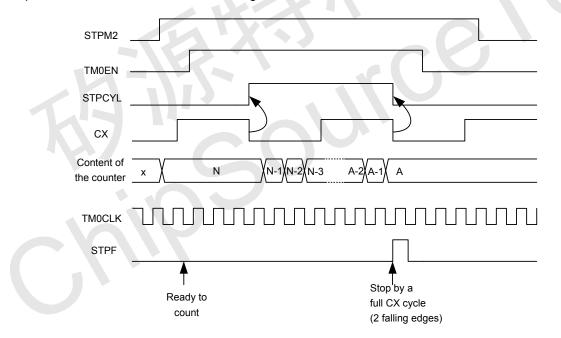

|      |       | 11.1.3 Timer0 Counting within a Full CX Cycle (STOP Mode 2)<br>11.1.4 Timer0 Counting within a Full Timer2 Clock Cycle (STOP Mode 3) |          |

|      |       |                                                                                                                                      |          |

| 12.  | ELE   | CTRICAL CHARACTERISTICS                                                                                                              | 41       |

|      | 12.1  | Absolute Maximum Rating                                                                                                              | 41       |

|      | 12.2  | DC Characteristics                                                                                                                   | 41       |

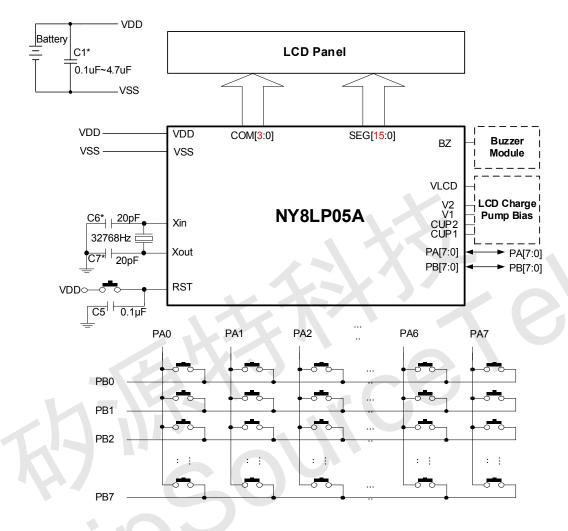

| 13.  | APP   | LICATION CIRCUITS                                                                                                                    | 43       |

|      | 13.1  | Application Circuit                                                                                                                  |          |

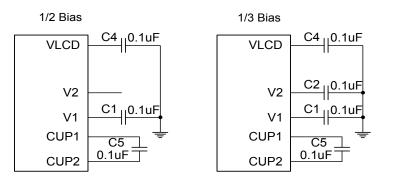

|      | 13.2  | LCD ChargePump Bias (VDD for VLCD/V2/V1)                                                                                             | 44       |

| 14.  | DIE   | PAD DIAGRAM                                                                                                                          |          |

ShenZhen ChipSourceTek Technology Co. , Ltd.

#### 1. 概述

NY8LP05A

NY8LP05A 爲高性能 8 位元 65C02 微控制器附加 LCD 驅動和 Buzzer 播放功能,三組 8位元 timer / counter, 16 根I/O。ROM 部份為崁入式 EPROM 架構的 OTP IC (One Time Programmable)。

MCU 為 CISC 架構易於編程和控制以及規劃到多種的應用。此外並提供多種工作模式 Slow mode, Standby mode 及 Halt mode (Sleep Mode) 來有效減少功耗。

#### 2. 功能

● 寬廣的工作電壓範圍: 1.5V應用, 1.1V~3.6V @ System clock ≤ 500KHz;

3.0V應用, 1.8V~3.6V @ System clock ≤ 4MHz。

- 4K-Byte OTP ROM •

- 64-Byte RAM •

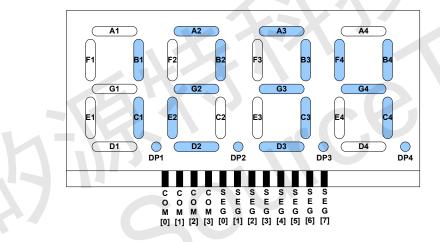

- LCD 點數 (COM x SEG):4 x 15。

- 16 GPIO,其中 6 根和 LCD SEG 共用

- 雙時脈振盪:系統時鐘可自由選擇高速或低速。

- ▶ 高速振盪: IOSC4M / IOSC2M / IOSC500K。

- ▶ 低速振盪: IOSC32K / XTAL32K。

- 內建高精準振盪線路(+/- 1.5%)。

- 四種工作模式可有效省電減少功耗:

- ➢ Normal mode、Slow mode、Standby mode 及 Halt mode。

- Normal mode 下 CPU clock 速度可程式化:

- > 可設定為高速振盪的 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128。

- 3 組 8 位元 Timer,可應用於1通道或2通道Buzzer或 RFC 等等應用。

- 支援大多數 LCD 顯示:

- > 1/2, 1/3 bias •

- ▶ 1/2, 1/3, 1/4 duty ∘

- 內建 Charge pump 升壓或 R-Bias 電阻分壓方式的電壓偏壓電路供應 LCD 顯示。

- 單顆電池應用的內部 RC 振盪器模式,LCD 幀速率最小值為 42Hz。

- RFC 功能,可用於温度、濕度偵測應用。

- 完整的系統保護,Watch-dog reset 看門狗重置功能及external reset pin 外部重置腳。

- 内建1.05V/1.15V/1.25V/1.3V(1.5V應用)或1.75V/1.85V/1.95V/2.00V(3V應用)的低電壓偵測。

NY8LP05A

ShenZhen ChipSourceTek Technology Co. , Ltd.

- 多樣化的 I/Os 設定: floating 輸入、pull-low 輸入、CMOS 輸出、open-drain 輸出。

- 1或2通道Buzzer。

- 6種中斷模式。

- LCD 點數組合:

| COMMON | SEGMENT | DOTS |

|--------|---------|------|

| 4      | 15      | 60   |

| 3      | 16      | 48   |

| 2      | 16      | 32   |

ShenZhen ChipSourceTek Technology Co. , Ltd.

#### 1. GENERAL DESCRIPTION

NY8LP05A is a high-performance 8-bit 65C02 micro-controller with LCD driver and buzzer output, three sets of 8-bit timer/counter, 16 general I/Os. It's embedded EPROM architecture OTP (One Time Programmable). For LCD driver, it applies for the most common-used LCD panels.

The CISC MCU architecture is very easy to program and control, various applications can be easily implemented. Furthermore, in addition to the Slow mode, it offers the Standby mode and Halt mode (Sleep mode) to minimize power dissipation.

#### 2. FEATURES

• Wide operating voltage range: For 1.5V application, 1.1V ~ 3.6V @ System clock ≤ 500KHz;

For 3.0V application,  $1.8V \sim 3.6V$  @ System clock  $\leq 4$ MHz.

- 4KB OTP ROM.

- 64B RAM.

- LCD Dots (COM x SEG): 4 x 15.

- 16 GPIO, 6 shared from LCD SEG.

- Dual-clock oscillation: System clock can switch between high oscillation and low oscillation.

- > High OSC: IOSC4M / IOSC2M / IOSC500K

- > Low OSC: IOSC32K / XTAL32K.

- Precisely embedded oscillator with build-in resistor (+/- 1.5%).

- Four kinds of operation mode to reduce system power consumption:

- > Normal mode, Slow mode, Standby mode and Halt mode.

- At Normal mode, CPU clock is software programmable.

- > 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128 of high oscillator (FFAOS) frequency.

- Three 8-bit timers for 1-channel or 2-channel buzzer or other applications such as RFC.

- Support most of LCD panel types:

- > 1/2, 1/3 bias.

- ➤ 1/2, 1/3, 1/4 duty.

- Charge pump or R-bias for the LCD display power.

- For internal RC oscillator mode with single battery applications, the LCD frame rate minimum value is 42Hz

- RFC-functioned block for the detection of humidity, temperature or other applications.

- Low voltage reset, watch-dog reset (by option) and external reset pin (by option) are all supported to protect the system.

NY8LP05A

- ShenZhen ChipSourceTek Technology Co. , Ltd.

- NY8LP05A 1.05V/1.15V/1.25V/1.3V(for 1.5V application) or 1.75V/1.85V/1.95V/2.00V(for 3V application) LVD flag for ٠ low battery detection.

- Flexible I/Os maximum with optional function: floating input, pull-low input, CMOS output, open-drain • output.

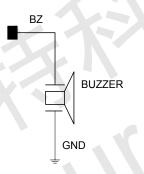

- 1-channel or 2-channel buzzer •

- 6 interrupt modes supported. •

- Possible LCD COM and SEG combination:

| COMMON | SEGMENT | DOTS |

|--------|---------|------|

| 4      | 15      | 60   |

| 3      | 16      | 48   |

| 2      | 16      | 32   |

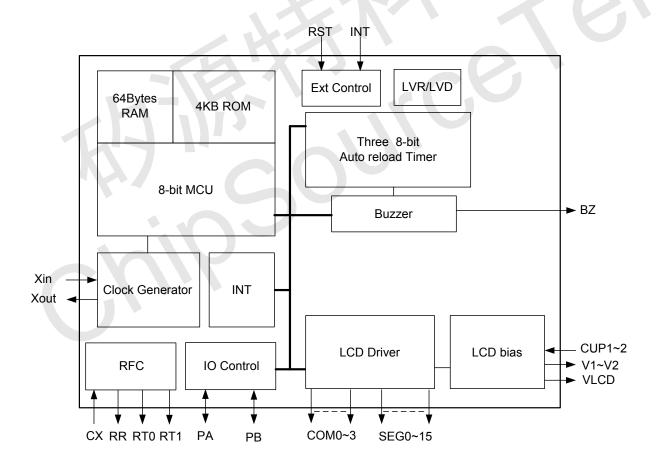

#### 3. **BLOCK DIAGRAM**

Fig.3-1: The block diagram

ShenZhen ChipSourceTek Technology Co. , Ltd.

## NY8LP05A

| Pad Name     | ATTR | Description                                                                 |

|--------------|------|-----------------------------------------------------------------------------|

| VDD          | Р    | Positive supply power.                                                      |

| VSS          | Ρ    | Negative supply power.                                                      |

| PA0/Xin      | I/O  | Bit 0 for Port A, or input of XTAL32K.                                      |

| PA1/Xout     | I/O  | Bit 1 for Port A, or output of XTAL32K.                                     |

| PA2/INT/Vpp  | I/O  | Bit 2 for Port A, or external interrupt input, or Vpp for programming.      |

| PA3/RST/Mode | I/O  | Bit 3 for Port A, or external reset input, or select programming mode.      |

| PA4/CX       | I/O  | Bit 4 for Port A, or input of RFC function.                                 |

| PA5/RR       | I/O  | Bit 5 for Port A, or output of RFC function.                                |

| PA6/RT0      | I/O  | Bit 6 for Port A, or output of RFC function.                                |

| PA7/RT1      | I/O  | Bit 7 for Port A, or output of RFC function.                                |

| PB0/BZ       | I/O  | Bit 0 for Port B, or buzzer output.                                         |

| PB1          | I/O  | Bit 1 for Port B.                                                           |

| SEG0/PB2/SDA | I/O  | LCD segment 0, Bit 2 for Port B, or serial data input at programming mode.  |

| SEG1/PB3/SCL | I/O  | LCD segment 1, Bit 3 for Port B, or serial clock input at programming mode. |

| SEG2/PB4     | I/O  | LCD segment 2, Bit 4 for Port B.                                            |

| SEG3/PB5     | I/O  | LCD segment 3, Bit 5 for Port B.                                            |

| SEG4/PB6     | 1/0  | LCD segment 4, Bit 6 for Port B.                                            |

| SEG5/PB7     | I/O  | LCD segment 5, Bit 7 for Port B.                                            |

| SEG6~14      | 0    | LCD segment 6~14.                                                           |

| COM0~3/SEG15 | 0    | LCD common 0~3 (COM3 can be used as SEG15).                                 |

| V1~2, VLCD   | Р    | LCD supply power.                                                           |

| CUP1~2       | I/O  | Auxiliary capacitor pins for voltage pumping.                               |

Total: 36 Pins

Legend: I = Input, O = Output, P = Power, A = Analog

ShenZhen ChipSourceTek Technology Co. , Ltd.

#### 5. Operation Modes

#### 5.1 Clock Source

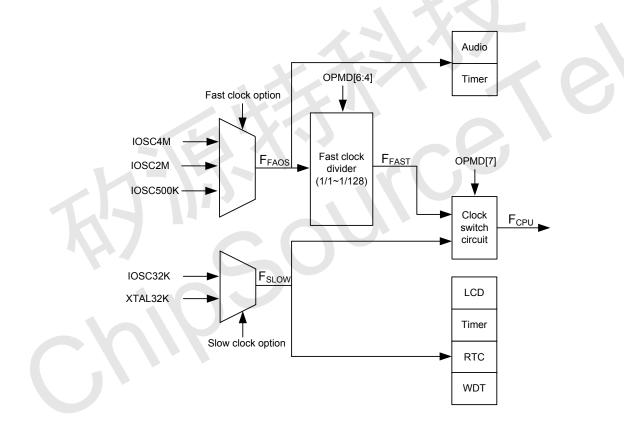

Because NY8LP05A is a dual-clock IC, there are fast oscillator ( $F_{FAOS}$ ) and slow oscillator ( $F_{SLOW}$ ) that can be selected as system oscillation ( $F_{CPU}$ ). The fast oscillator which could be used as  $F_{FAOS}$  is internal high RC oscillator: IOSC4M, IOSC2M and IOSC500K. The slow oscillators which could be used as  $F_{SLOW}$  are internal low RC oscillator (IOSC32K) or external low crystal oscillator (XTAL32K). Users can choose the clock sources by programming its option based on the application.

To utilize the precise timing application, two pins (Xin & Xout) are needed to connect with external crystal module and set the corresponding option for 32KHz crystal. To match the high-speed application, it provides up to 4MHz for  $F_{CPU}$  and no additional pins are needed.

#### Figure 5-1 Oscillation Configuration

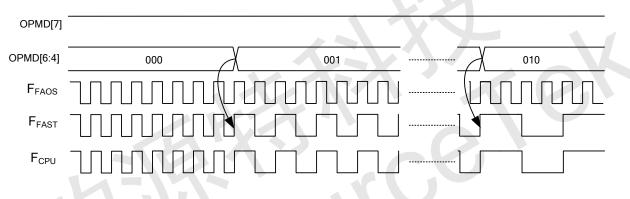

The fast frequency (F<sub>FAST</sub>) is divided from F<sub>FAOS</sub> through control register OPMD[6:4]: 1/1~1/128. The F<sub>SLOW</sub> is the slow frequency and the source of Real-Time-Clock (RTC). The RTC is the clock source of 14-bit divider, ranges from 16KHz to 2Hz, and it generates multiple clocks to apply to the LCD module, LCD power charge pump block, watch dog timer, and etc. Therefore user is suggested to enable the RTC (OPMD[3]) when CPU is busy. Besides, the RTC counter can be cleared by writing 0 to OPMD[2], and which is always read as high.

|                |                                   |            |                                                                                                                       | NIVOL DOE A                          |

|----------------|-----------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Mode           | Normal mode                       | Slow mode  | Standby mode                                                                                                          | Halt mode                            |

| Fcpu           | ON (Ffast)                        | ON (Fslow) | OFF                                                                                                                   | OFF                                  |

| Ffaos          | ON                                | OFF        | OFF                                                                                                                   | OFF                                  |

| Ffast          | F <sub>FAOS</sub> /2 <sup>N</sup> | OFF        | OFF                                                                                                                   | OFF                                  |

| Fslow          | ON/OFF                            | ON         | ON                                                                                                                    | OFF                                  |

| RTC            | ON/OFF                            | ON         | ON                                                                                                                    | OFF                                  |

| LCD            | ON/OFF                            | ON/OFF     | ON/OFF                                                                                                                | OFF                                  |

| Wake-up Source |                                   |            | - Key change<br>- Timer2/Timer1/<br>Timer0 Interrupt<br>(based on Fs∟ow)<br>- FT/ST Interrupt<br>- External Interrupt | - Key change<br>- External Interrupt |

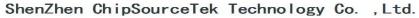

NY8LP05A provide four kinds of operating mode to tailor all kinds of application and save power consumptions. These operating modes are Normal mode, Slow mode, Standby mode and Halt mode. Normal mode is designated for high-speed operating mode. Slow mode is designated for low-speed mode in order to save power consumption. At Standby mode, NY8LP05A will stop almost all operations except Timer2 /Timer1 /Timer0 /FT /ST (based on F<sub>SLOW</sub>) in order to wake up periodically. At Halt mode, NY8LP05A will sleep until key change or external interrupt occurs. User can set the control register OPMD to swap Normal/Slow mode and the control register SLP to enter Standby/Halt mode. The block diagram of four operating modes is described in Figure 2-2.

ShenZhen ChipSourceTek Technology Co. , Ltd.

#### 5.2 Normal Mode

After any reset event is occurred and reset process is complete, NY8LP05A will enter Normal mode. At Normal mode, F<sub>FAOS</sub> is selected as system oscillation in order to provide highest performance and its power consumption will be the largest among four operating modes.

- Instruction execution is based on F<sub>FAST</sub> and all peripheral modules may be active according to corresponding module enable bit.

- FFAST is divided from the FFAOS (1/1 ~ 1/128).

- F<sub>SLOW</sub> is enabled, or disabled according to application.

- IC can switch to Slow mode by writing 0 to the bit7 of control register OPMD (\$17[7]).

- IC can switch to Standby mode or Halt mode by programming control register SLP (\$15) with 0x5A.

Figure 5-3: The procedure of dividing CPU clock

Users have to set the control register OPMD to the relative setting as the following table.

| Addr. | Name | R/W         | Bit       | Data  | Description                                 | Default                                   |      |

|-------|------|-------------|-----------|-------|---------------------------------------------|-------------------------------------------|------|

| CX    |      | W           | [2]       | 0     | Write 0 to clear RTC counter (read as high) | х                                         |      |

|       |      |             | [3]       | 1/0   | RTC Enable/Disable                          | Enable                                    |      |

|       |      |             |           | 000   | F <sub>FAST</sub> = F <sub>FAOS</sub> /1    |                                           |      |

|       |      |             |           | 001   | Ffast = Ffaos/2                             |                                           |      |

|       |      | OPMD<br>R/W |           | 010   | Ffast = Ffaos/4                             |                                           |      |

| \$17  | OPMD |             |           | [6·4] | 011                                         | Ffast = Ffaos/8                           | E /1 |

|       |      |             | R/W [6:4] | 100   | Ffast = Ffaos/16                            | F <sub>FAOS</sub> /1                      |      |

|       |      |             |           |       | 101                                         | F <sub>FAST</sub> = F <sub>FAOS</sub> /32 |      |

|       |      |             |           |       | 110                                         | FFAST = FFAOS/64                          |      |

|       |      |             |           | 111   | FFAST = FFAOS/128                           |                                           |      |

|       |      |             | [7]       | 1/0   | FCPU = FFAST/FSLOW (32KHZ)                  | Ffast                                     |      |

Note1: It needs to be cautious to use OPMD to divide the clock frequency. Please refer to AP-Note 34 for details.

*Note:*2 *F*<sub>FAST</sub> should NOT be slower than 16KHz *Ex: If fast clock source is IOSC500K, F*<sub>FAOS</sub>/32, *F*<sub>FAOS</sub>/64 and *F*<sub>FAOS</sub>/128 should not be selected.

ShenZhen ChipSourceTek Technology Co. , Ltd.

#### 5.3 Slow Mode

# NY8LP05A

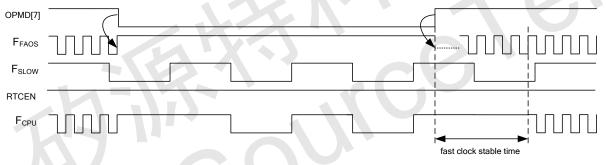

NY8LP05A will enter Slow mode by writing 0 to the bit7 of control register OPMD (\$17[7]). At Slow mode, F<sub>SLOW</sub> is selected as system oscillation in order to save power consumption but still keep IC running. However, the F<sub>FAOS</sub> should be turned off permanently if the mode won't be swapped to Normal mode. When switching to Normal mode, the fast clock source must wait about 512 cycles (~128us@4MHz) for being stable. It is strongly recommended that IC should switch to Slow mode after F<sub>SLOW</sub> being stable (~120us@IOSC32K or ~30ms@XTAL32K). Once setting control register SLP (\$15) with 0x5A, it will turn to Standby mode or Halt mode, and the FCPU will be stopped until the wake-up signal occurs.

- Instruction execution is based on FSLOW and all peripheral modules may be active according to corresponding module enable bit.

- FFAOS can be turned off by writing 0 to OPMD[7].

- IC can switch to Standby mode or Halt mode by programming control register SLP (\$15) with 0x5A.

- IC can switch to Normal mode by writing 1 to OPMD[7].

Figure 5-4: The procedure of switching operation modes

#### 5.4 Standby Mode

By setting control register SLP (\$15) with 0x5A, the operation mode will turn to Standby mode if RTC is enabled (OPMD[3] = 1), while the previous mode is either Normal mode or Slow mode. At Standby mode, the  $F_{FAOS}$  is shut down and the  $F_{SLOW}$  is kept to supply the clock for LCD display, etc.

NY8LP05A supports two wake-up methods to leave out of Standby mode, the difference between I/O pads and its data registers (key change), the occurrence of each interrupt, So before entering Standby mode, users have to keep in mind to store the current input port statuses into port registers,- If the system is waked up, the succeeding instructions after writing SLP register will be executed after the clock source stable time. The stable time of fast clock source should wait about 512 cycles (~128us@4MHz), and the stable time of IOSC32K is about 4 cycles (~120us@32KHz), the stable time of XTAL32K is about 1024 cycles (~30ms@32KHz).

If the IC is waked up from Standby mode by a reset pin, it goes into reset procedure.

- Instruction execution is stop and some peripheral modules may be active according to corresponding module enable bit.

- FFAOS can be shut down by writing 0x5A to register SLP (\$15).

- The FSLOW is still active and running.

- IC can being waked up from Standby mode if any of (a) key change wake-up (refer to 7.1 I/O Ports), (b)

Timer2/Timer1/Timer0 (based on FSLOW) interrupt, (c) FT/ST interrupt, (d) external interrupt.

- After being waked up from Standby mode, IC will return to Normal mode if OPMD[7] = 1, or Slow mode if OPMD[7] = 0.

The relative control registers are shown as the following tables

| Addr. | Name | R/W | Bit   | Data | Description         | Default |

|-------|------|-----|-------|------|---------------------|---------|

| \$15  | SLP  | W   | [7:0] |      | Write 0x5A to sleep | xx      |

#### 5.5 Halt mode

By setting control register SLP (\$15) with 0x5A, the operation mode will turn to Halt mode if RTC is disabled (OPMD[3] = 0), while the previous mode is either Normal mode or Slow mode. Halt mode is also known as Sleep mode. As implied by the name, the IC falls asleep and the system clock is completely turned off, so all the IC functions are halted and it minimizes the power consumption.

At Halt mode, both of the F<sub>FAOS</sub> and the F<sub>SLOW</sub> are shut down and waked up by key change or external interrupt. So before entering Halt mode, users have to keep in mind to store the current input port statuses into port registers. For avoiding awaking Halt mode wrongly,-, and the data register (PX) must be cleared to low. If the system is waked up, the succeeding instructions after writing SLP register will be executed after the clock source stable time.

If the IC is waked up from the standby mode by a reset pin, it goes into the reset procedure.

- Instruction execution is stop and all peripheral modules are disabled.

- FFAOS and FSLOW are both disabled automatically.

- IC can being waked up from Halt mode if any of (a) Key change wake-up (refer to 7.1 I/O Ports) or (b) external interrupt is happened.

- After being waked up from Halt mode, IC will return to Normal mode if OPMD[7] = 1, or Slow mode if OPMD[7] = 0.

The relative control registers are shown as the following tables:

| Addr. | Name | R/W | Bit   | Data | Description         | Default |

|-------|------|-----|-------|------|---------------------|---------|

| \$15  | SLP  | W   | [7:0] |      | Write 0x5A to sleep | хх      |

ShenZhen ChipSourceTek Technology Co. , Ltd.

#### 6. System Control

#### 6.1 Reset System

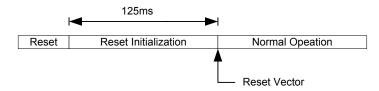

For the NY8LP05A IC, the reset procedure needs at least 125ms to deal with initialization process. In addition, 4 conditions will cause the reset procedure to be triggered, described in next sections. The reset initialization procedure is shown in Figure 3-1.

Figure 6-1: The reset initialization procedure

#### 6.1.1 Power-On Reset (POR)

After power-on, the power-on reset initialization will automatically be set out. After the system leaves the reset initialization procedure, it enters the normal operation and the program counter (PC) starts at the reset vector.

#### 6.1.2 Low Voltage Reset (LVR)

When the system enters the normal operation, the power supply voltage must be kept in an effective working voltage range. When the power supply voltage is lower than the effective operating voltage range, the system can't work properly. When the detector detects a harmful low voltage supply, it will cause a low voltage reset.

#### 6.1.3 External Reset Pin (by option)

The external reset pin is always pulled-low with strong or weak resistor controlled by option. Generally, when the reset pin rises to high, it generates an external reset.

#### 6.1.4 Watch-Dog Timer Reset (WDTR) (by option)

To recover from program malfunction, the NY8LP05A IC supports an embedded watch-dog timer reset by option. The WDTR function is based on Real-Time-Clock, and always works with the program executing. Users have to clear the WDT (\$16) periodically to prevent from timing up with a reset generation. Typically, the minimum time-up period of the WDT is about 1.5s.

Users can write 0xA5 to the control register WDGC to clear WDT, The relative control registers are shown as the following tables.

| Addr. | Name | R/W | Bit   | Data | Description                        | Default |

|-------|------|-----|-------|------|------------------------------------|---------|

| \$16  | WDGC | W   | [7:0] |      | Write 0xA5 to clear watchdog timer | хх      |

#### 6.1.5 Low Voltage Detector (LVD)

# NY8LP05A

To monitor the voltage supply, the NY8LP05A also provides low voltage detector (LVD) function. The LVD is fixed as 1.1V for 1.5V application and 1.85V for 3.0V application. If LVD is enabled, user can read back LVD status, which will go high when the power supply is lower than LVD level. The setting of LVD is shown as below.

| Addr. | Name | R/W        | Bit   | Data | Description                                          | Default |  |  |  |     |     |     |                    |         |

|-------|------|------------|-------|------|------------------------------------------------------|---------|--|--|--|-----|-----|-----|--------------------|---------|

|       |      |            | [1:0] | 00   | LVD level = 1.05V or 1.75V*                          |         |  |  |  |     |     |     |                    |         |

|       | LVD  | R/W<br>LVD |       | 01   | LVD level = 1.15V or 1.85V*                          | 00      |  |  |  |     |     |     |                    |         |

| ¢10   |      |            |       | 10   | LVD level = 1.25V or 1.95V*                          | 00      |  |  |  |     |     |     |                    |         |

| \$1C  |      |            |       | 11   | LVD level = 1.3V or 2.0V*                            |         |  |  |  |     |     |     |                    |         |

|       |      |            |       |      |                                                      |         |  |  |  | R/W | [4] | 1/0 | LVD Enable/Disable | Disable |

|       |      | R          | [7]   | 1/0  | LVD status: VDD <lvd level="" vdd="">LVD level</lvd> | x       |  |  |  |     |     |     |                    |         |

\*Depends on 1.5V or 3V application option

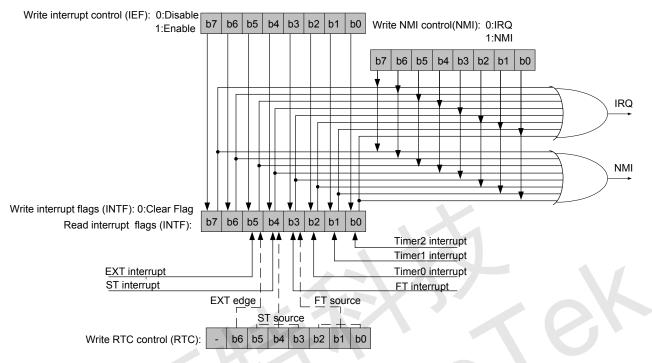

#### 6.2 Interrupts

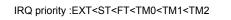

The interrupt event can be a fixed interval of the Timer2/Timer1/Timer0, the fast real timer (FT), the slow real timer (ST), a random period triggered by the external interrupt pin (INT), The Timer1/Timer0 can also be selected as one of the sample rate for audio playing,. There are two real timers (FT & ST) in the NY8LP05A IC, which function as long as it isn't in the halt mode. NY8LP05A provide 8 fixed intervals from the real timer for FT, ranged from 16Hz to 16KHz, and it provide 8 fixed intervals from the real timer for ST, ranged from 256Hz to 2Hz. The interrupt events have to be cleared by users after entering the interrupt routine.

While any of hardware interrupts is occurred, the corresponding bit of interrupt flag register INTF will be set to 1. This bit will not be clear until users write 0 to this bit. Therefore user can obtain information of which event causes hardware interrupt by polling register INTF even if interrupt enable flag register IEF is Disable. The detailed settings of interrupt mode and flag are shown as the following tables.

| Addr.    | Name | R/W | Bit | Data                                                                   | Description                     | Default |     |     |                            |   |

|----------|------|-----|-----|------------------------------------------------------------------------|---------------------------------|---------|-----|-----|----------------------------|---|

|          |      |     | [0] | 1/0                                                                    | Timer2 Interrupt Enable/Disable | Disable |     |     |                            |   |

|          |      |     | [1] | 1/0                                                                    | Timer1 Interrupt Enable/Disable | Disable |     |     |                            |   |

| \$0C IEF | R/W  | [2] | 1/0 | Timer0 Interrupt Enable/Disable<br>(or Timer0 stop@Timer0 stop enable) | Disable                         |         |     |     |                            |   |

|          |      |     | [3] | 1/0                                                                    | FT Interrupt Enable/Disable     | Disable |     |     |                            |   |

|          |      |     | [4] | 1/0                                                                    | ST Interrupt Enable/Disable     | Disable |     |     |                            |   |

|          |      |     | [5] | 1/0                                                                    | EXT Interrupt Enable/Disable    | Disable |     |     |                            |   |

|          |      | R   | [0] | 1/0                                                                    | Read Timer2 Interrupt Flag      | 0       |     |     |                            |   |

|          |      |     | R   | R                                                                      | R                               | R       | [1] | 1/0 | Read Timer1 Interrupt Flag | 0 |

| \$0D     | INTF |     |     |                                                                        |                                 |         | R   | R   | R                          | R |

|          |      |     | [3] | 1/0                                                                    | Read FT Interrupt Flag          | 0       |     |     |                            |   |

|          |      |     | [4] | 1/0                                                                    | Read ST Interrupt Flag          | 0       |     |     |                            |   |

|          |      |     | [5] | 1/0                                                                    | Read EXT Interrupt Flag         | 0       |     |     |                            |   |

ShenZhen ChipSourceTek Technology Co. , Ltd.

| Addr.    | Name | R/W      | Bit   | Data | Description NY8                                                         | LP05A<br>Default                                                   |

|----------|------|----------|-------|------|-------------------------------------------------------------------------|--------------------------------------------------------------------|

|          |      |          | [0]   | 0    | Clear Timer2 Interrupt Flag                                             | 0                                                                  |

|          |      | W        | [1]   | 0    | Clear Timer1 Interrupt Flag                                             | 0                                                                  |

|          |      |          | W     | [2]  | 0                                                                       | Clear Timer0 Interrupt Flag<br>(or Timer0 stop@Timer0 stop enable) |

|          |      |          | [3]   | 0    | Clear FT Interrupt Flag                                                 | 0                                                                  |

|          |      |          | [4]   | 0    | Clear ST Interrupt Flag                                                 | 0                                                                  |

|          |      |          | [5]   | 0    | Clear EXT Interrupt Flag                                                | 0                                                                  |

|          |      |          | [0]   | 1/0  | Timer2 Interrupt Flag be NMI/IRQ                                        | IRQ                                                                |

|          |      |          | [1]   | 1/0  | Timer1 Interrupt Flag be NMI/IRQ                                        | IRQ                                                                |

| \$0E NMI | NMI  | R/W      | [2]   | 1/0  | Timer0 Interrupt Flag be NMI/IRQ<br>(or Timer0 stop@Timer0 stop enable) | IRQ                                                                |

|          |      |          | [3]   | 1/0  | FT Interrupt Flag be NMI/IRQ                                            | IRQ                                                                |

|          |      |          | [4]   | 1/0  | ST Interrupt Flag be NMI/IRQ                                            | IRQ                                                                |

|          |      |          | [5]   | 1/0  | EXT Interrupt Flag be NMI/IRQ                                           | IRQ                                                                |

|          |      |          |       | 000  | FT Interrupt = RT[10] (16Hz, FsLow/2048)                                |                                                                    |

|          |      |          | [2:0] | 001  | FT Interrupt = RT[8] (64Hz, FsLow/512)                                  |                                                                    |

|          |      |          |       | 010  | FT Interrupt = RT[6] (256Hz, FsLow/128)                                 | RT[4]                                                              |

|          |      |          |       | 011  | FT Interrupt = RT[4] (1KHz, FsLow/32)                                   |                                                                    |

|          |      |          |       | 100  | FT Interrupt = RT[3] (2KHz, FsLow/16)                                   |                                                                    |

|          |      |          |       | 101  | FT Interrupt = RT[2] (4KHz, FsLow/8)                                    |                                                                    |

|          |      |          |       | 110  | FT Interrupt = RT[1] (8KHz, FsLow/4)                                    |                                                                    |

|          |      |          |       | 111  | FT Interrupt = RT[0] (16KHz, FsLow/2)                                   |                                                                    |

| \$0F     | RTC  | R/W      |       | 000  | ST Interrupt = RT[13] (2Hz, F <sub>SLOW</sub> /16384)                   |                                                                    |

|          |      |          |       | 001  | ST Interrupt = RT[12] (4Hz, F <sub>SLOW</sub> /8192)                    |                                                                    |

|          |      |          |       | 010  | ST Interrupt = RT[11] (8Hz, F <sub>SLOW</sub> /4096)                    |                                                                    |

|          |      | <i>v</i> | [5:3] | 011  | ST Interrupt = RT[10] (16Hz, FsLow/2048)                                | DT[12]                                                             |

|          |      |          | [5.5] | 100  | ST Interrupt = RT[9] (32Hz, F <sub>SLOW</sub> /1024)                    | RT[13]                                                             |

|          |      |          |       | 101  | ST Interrupt = RT[8] (64Hz, F <sub>SLOW</sub> /512)                     |                                                                    |

|          |      |          |       | 110  | ST Interrupt = RT[7] (128Hz, F <sub>SLOW</sub> /256)                    |                                                                    |

|          |      |          |       | 111  | ST Interrupt = RT[6] (256Hz, F <sub>SLOW</sub> /128)                    |                                                                    |

|          |      |          | [6]   | 1/0  | EXT Interrupt takes place at Rising/Falling edge                        | Rising                                                             |

Note: It is strongly recommended to set Timer2, Timer1, Timer0, FT, ST, external interrupt, control register before enabling interrupt, otherwise interrupt may be falsely triggered.

For example, if a Timer2 interrupt occurs, the IC pushes the program counter (PC) to stack (STK), and jump to the interrupt vector (\$7E0) automatically. In the interrupt sub-routine, user must store the accumulator (ACC), register X/Y (X/Y), and draw the Y, X, and ACC back before Timer2 sub-routine being finished. With the return instruction executes, the interrupt routine is finished. The IC pops STK back to the PC, and back to the original track of the program. The addresses for each interrupt mode are described in below table.

| Addr. | Interrupt Vector | IRQ Priority |  |  |

|-------|------------------|--------------|--|--|

| \$7E0 | Timer2 Interrupt | 1 (highest)  |  |  |

| \$7E2 | Timer1 Interrupt | 2            |  |  |

| \$7E4 | Timer0 Interrupt | 3            |  |  |

| \$7E6 | FT Interrupt     | 4            |  |  |

| \$7E8 | ST Interrupt     | 5            |  |  |

| \$7EA | EXT Interrupt    | 6            |  |  |

| \$7EC |                  | 7            |  |  |

| \$7EE |                  | 8 (lowest)   |  |  |

The Timer2 interrupt sub-routine is shown below.

V-IRQ-Timer2: PHA PHX PHY PLY PLX PLA RTI

The NY8LP05A IC supports two types of interrupt mode, IRQ and NMI (Non-Maskable Interrupt). The IRQ mode is sensed by **level-trigger** event, which means the continued interrupt event will be held until the current is finished. Even if two interrupt events come up simultaneously, the priority of each interrupt decides that the event with higher priority defined by IC itself will be enabled. The NMI mode is sensed by **edge-trigger** event, if an event is coming up with the others at the same time. There is the only one with highest priority defined by software will be enabled and the others may be falsely omitted, **so it is strongly recommended to enable** <u>ONLY ONE of NMI (\$0E)</u>.

ShenZhen ChipSourceTek Technology Co. , Ltd.

NY8LP05A

Figure 6-2: The structure of IRQ & NMI

ShenZhen ChipSourceTek Technology Co. , Ltd.

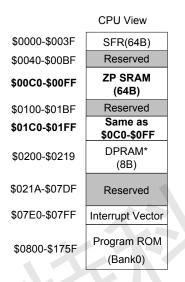

#### 7. Address Mapping

In the NY8LP05A IC, SFR contains 64 bytes, RAM contains 64 bytes for zero page register (ZP) and stack (STK). Moreover, there are 4K bytes ROM for program data. The following three sections describe the detail about special function register (SFR), RAM and ROM configuration of the NY8LP05A.

#### 7.1 Control Register Description

The special function register (SFR) is assigned to use the dedicated address ranged \$0000 to \$0039. Users can program these registers to fit their applications. The SFR table is shown below.

| Addr.       | Name | R/W | Bit   | Data | Description                                           | Default |

|-------------|------|-----|-------|------|-------------------------------------------------------|---------|

| \$00        |      | R   | [7:0] |      | Read the Timer0 counting data[7:0]                    | ХХ      |

| <b>Ф</b> ОО | TM0D | W   | [7:0] |      | Preload Timer0 data[7:0]                              | ХХ      |

| 1           |      |     |       | 000x | Timer0 clock = CX                                     |         |

|             |      |     |       | 001x | Timer0 clock = RT[13] (2Hz, F <sub>SLOW</sub> /16384) |         |

|             |      |     |       | 0100 | Timer0 clock = RT[11] (8Hz, F <sub>SLOW</sub> /4096)  |         |

|             |      |     |       | 0101 | Timer0 clock = RT[9] (32Hz, F <sub>SLOW</sub> /1024)  |         |

|             |      |     |       | 0110 | Timer0 clock = RT[7] (128Hz, F <sub>SLOW</sub> /256)  |         |

|             |      |     |       | 0111 | Timer0 clock = RT[5] (512Hz, F <sub>SLOW</sub> /64)   |         |

|             |      |     | 10.01 | 1000 | Timer0 clock = BT[6] (F <sub>FAOS</sub> /128)         |         |

| ¢01         | TMOC |     | [3:0] | 1001 | Timer0 clock = BT[5] (F <sub>FAOS</sub> /64)          | BT[0]   |

| \$01        | TM0C | R/W |       | 1010 | Timer0 clock = BT[4] (F <sub>FAOS</sub> /32)          |         |

|             |      |     |       | 1011 | Timer0 clock = BT[3] (F <sub>FAOS</sub> /16)          |         |

|             |      |     |       | 1100 | Timer0 clock = BT[2] (F <sub>FAOS</sub> /8)           |         |

|             |      |     |       | 1101 | Timer0 clock = BT[1] (F <sub>FAOS</sub> /4)           |         |

|             |      |     |       | 1110 | Timer0 clock = BT[0] (F <sub>FAOS</sub> /2)           |         |

|             |      |     |       | 1111 | Timer0 clock = F <sub>FAOS</sub>                      |         |

|             |      |     | [4]   | 1/0  | Timer0 Reload/One shot                                | 1       |

|             |      |     | [5]   | 1/0  | Tone0 Enable/Disable                                  | Enable  |

NY8LP05A

| Addr.       | Name  | R/W     | Bit   | Data | Description NY8L                                                       | Default |

|-------------|-------|---------|-------|------|------------------------------------------------------------------------|---------|

|             |       |         |       | 00   | Timer0 clock stop mode OFF                                             |         |

|             |       |         | [7.0] | 01   | Timer0 clock stopped by Timer2 overflow                                |         |

|             |       |         | [7:6] | 10   | Timer0 clock stopped by a full cycle of CX                             | OFF     |

|             |       |         |       | 11   | Timer0 clock stopped by a full cycle of Timer2 clock                   |         |

| \$02        | TM0EN | R/W     | [0]   | 1/0  | Timer0 Enable/Disable                                                  | Disable |

| <b>AO</b> 4 | TMAD  | R       | [7:0] |      | Read the Timer1 counting data[7:0]                                     | ХХ      |

| \$04        | TM1D  | W       | [7:0] |      | Preload Timer1 data[7:0]                                               | ХХ      |

|             |       |         |       | 000x | Timer1 clock = TM0D[7]                                                 |         |

|             |       |         |       | 001x | Timer1 clock = RT[13] (2Hz, F <sub>SLOW</sub> /16384)                  |         |

|             |       |         |       | 0100 | Timer1 clock = RT[11] (8Hz, F <sub>SLOW</sub> /4096)                   |         |

|             |       |         |       | 0101 | Timer1 clock = RT[9] (32Hz, F <sub>SLOW</sub> /1024)                   |         |

|             |       |         |       | 0110 | Timer1 clock = RT[7] (128Hz, F <sub>sLow</sub> /256)                   |         |

|             |       |         |       | 0111 | Timer1 clock = RT[5] (512Hz, F <sub>sLow</sub> /64)                    |         |

|             |       |         |       | 1000 | Timer1 clock = BT[6] (F <sub>FAOS</sub> /128)                          |         |

| \$05        | TM1C  | R/W     | [3:0] | 1001 | Timer1 clock = BT[5] (F <sub>FAOS</sub> /64)                           | BT[0]   |

|             |       |         |       | 1010 | Timer1 clock = BT[4] (FFAOS/32)                                        |         |

|             |       |         |       | 1011 | Timer1 clock = BT[3] (F <sub>FAOS</sub> /16)                           |         |

|             |       |         |       | 1100 | Timer1 clock = BT[2] (F <sub>FAOS</sub> /8)                            |         |

|             |       |         |       | 1101 | Timer1 clock = BT[1] (F <sub>FAOS</sub> /4)                            |         |

|             |       |         |       | 1110 | Timer1 clock = $BT[0]$ (F <sub>FAOS</sub> /2)                          |         |

|             |       |         |       | 1111 | Timer1 clock = F <sub>FAOS</sub>                                       | -       |

|             |       |         | [4]   | 1/0  | Timer1 Reload/One shot                                                 | 1       |

| \$06        | TM1EN | R/W     | [0]   | 1/0  | Timer1 Enable/Disable                                                  | Disable |

|             |       | R       | [7:0] |      | Read the Timer2 counting data[7:0]                                     | XX      |

| \$08        | TM2D  | W       | [7:0] |      | Preload Timer2 data[7:0]                                               | XX      |

|             |       |         |       | 000x | Timer2 clock = TM1D[7]                                                 |         |

|             |       |         |       | 001x | Timer2 clock = RT[13] (2Hz, F <sub>SLOW</sub> /16384)                  | -       |

|             |       |         |       | 0100 | Timer2 clock = RT[11] (8Hz, F <sub>SLOW</sub> /4096)                   | -       |

|             |       |         |       | 0101 | Timer2 clock = RT[9] (32Hz, FsLow/1024)                                | -       |

|             |       |         |       | 0110 | Timer2 clock = $RT[7]$ (128Hz, F <sub>SLOW</sub> /256)                 | -       |

|             |       |         |       | 0111 | Timer2 clock = $RT[5]$ (512Hz, FsLow/64)                               | 1       |

|             |       |         |       | 1000 | Timer2 clock = BT[8] ( $F_{FAOS}/512$ )                                | -       |

| \$09        | TM2C  | R/W     | [3:0] | 1001 | Timer2 clock = $BT[7]$ (FFAOS/256)                                     | BT[2]   |

| 115         |       |         |       | 1010 | Timer2 clock = $BT[6]$ (FFAOS/128)                                     | 1       |

|             |       |         |       | 1011 | Timer2 clock = $BT[5]$ (F <sub>FAOS</sub> /64)                         | -       |

|             |       |         |       | 1100 | Timer2 clock = $BT[4]$ (F <sub>FAOS</sub> /32)                         | -       |

|             |       |         |       | 1101 | Timer2 clock = $BT[3]$ (FFAOS/16)                                      | -       |

|             |       |         |       | 1110 | Timer2 clock = $BT[2]$ (FFAOS/8)                                       | -       |

|             |       |         |       | 1111 | Timer2 clock = $BT[2]$ (FrA05/0)<br>Timer2 clock = $BT[1]$ (FrA05/4)   | -       |

|             |       |         | [4]   | 1/0  | Timer2 Reload/One shot                                                 | 1       |

| \$0A        | TM2EN | R/W     | [4]   | 1/0  | Timer2 Enable/Disable                                                  | Disable |

| ψυΛ         |       | 1.7.4.6 | [0]   | 1/0  | Timer2 Interrupt Enable/Disable                                        | Disable |

|             |       |         | [0]   | 1/0  | Timer1 Interrupt Enable/Disable                                        | Disable |

|             |       |         | [']   | 1/0  |                                                                        | Disable |

| \$0C        | IEF   | R/W     | [2]   | 1/0  | Timer0 Interrupt Enable/Disable<br>(or Timer0 stop@Timer0 stop enable) | Disable |

| Addr.       | Name | ame R/W |       | Data | Description NY8                                                    | Default             |       |                                                                         |                                                    |  |  |     |                                                      |  |

|-------------|------|---------|-------|------|--------------------------------------------------------------------|---------------------|-------|-------------------------------------------------------------------------|----------------------------------------------------|--|--|-----|------------------------------------------------------|--|

|             |      |         | [4]   | 1/0  | ST Interrupt Enable/Disable                                        | Disable             |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [5]   | 1/0  | EXT Interrupt Enable/Disable                                       | Disable             |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [0]   | 1/0  | Read Timer2 Interrupt Flag                                         | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [1]   | 1/0  | Read Timer1 Interrupt Flag                                         | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [2]   | 1/0  | Read Timer0 Interrupt Flag                                         | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      | R       |       |      | (or Timer0 stop@Timer0 stop enable)                                |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [3]   | 1/0  | Read FT Interrupt Flag                                             | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [4]   | 1/0  | Read ST Interrupt Flag                                             | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

| \$0D        | INTF |         | [5]   | 1/0  | Read EXT Interrupt Flag                                            | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [0]   | 0    | Clear Timer2 Interrupt Flag                                        | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [1]   | 0    | Clear Timer1 Interrupt Flag                                        | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      | w       | [2]   | 0    | Clear Timer0 Interrupt Flag<br>(or Timer0 stop@Timer0 stop enable) | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [3]   | 0    | Clear FT Interrupt Flag                                            | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [4]   | 0    | Clear ST Interrupt Flag                                            | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [5]   | 0    | Clear EXT Interrupt Flag                                           | 0                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [0]   | 1/0  | Timer2 Interrupt Flag be NMI/IRQ                                   | IRQ                 |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      | R/W     | [1]   | 1/0  | Timer1 Interrupt Flag be NMI/IRQ                                   | IRQ                 |       |                                                                         |                                                    |  |  |     |                                                      |  |

| \$0E NMI    | NMI  |         | R/W   | R/W  | R/W                                                                | [2]                 | 1/0   | Timer0 Interrupt Flag be NMI/IRQ<br>(or Timer0 stop@Timer0 stop enable) | IRQ                                                |  |  |     |                                                      |  |

| <b>*</b> *- |      |         | [3]   | 1/0  | FT Interrupt Flag be NMI/IRQ                                       | IRQ                 |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [4]   | 1/0  | ST Interrupt Flag be NMI/IRQ                                       | IRQ                 |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [5]   | 1/0  | EXT Interrupt Flag be NMI/IRQ                                      | IRQ                 |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 000  | FT Interrupt = RT[10] (16Hz, F <sub>SLOW</sub> /2048)              |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 001  | FT Interrupt = RT[8] (64Hz, FsLow/512)                             |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       |      |                                                                    |                     |       |                                                                         |                                                    |  |  | 010 | FT Interrupt = RT[6] (256Hz, F <sub>SLOW</sub> /128) |  |

|             |      |         |       |      |                                                                    |                     | [2:0] | 011                                                                     | FT Interrupt = RT[4] (1KHz, F <sub>SLOW</sub> /32) |  |  |     |                                                      |  |

|             |      |         |       |      |                                                                    | [2:0]               | 100   | FT Interrupt = RT[3] (2KHz, F <sub>SLOW</sub> /16)                      | RT[4]                                              |  |  |     |                                                      |  |

|             |      |         |       |      |                                                                    |                     |       | 101                                                                     | FT Interrupt = RT[2] (4KHz, F <sub>SLOW</sub> /8)  |  |  |     |                                                      |  |

|             |      |         |       | 110  | FT Interrupt = RT[1] (8KHz, F <sub>SLOW</sub> /4)                  | 1                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 111  | FT Interrupt = RT[0] (16KHz, F <sub>SLOW</sub> /2)                 | -                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

| \$0F        | RTC  | R/W     |       | 000  | ST Interrupt = RT[13] (2Hz, F <sub>SLOW</sub> /16384)              |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 001  | ST Interrupt = RT[12] (4Hz, F <sub>SLOW</sub> /8192)               | 1                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 010  | ST Interrupt = RT[11] (8Hz, F <sub>SLOW</sub> /4096)               | 1                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [5:0] | 011  | ST Interrupt = RT[10] (16Hz, F <sub>SLOW</sub> /2048)              |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             | 1    |         | [5:3] | 100  | ST Interrupt = RT[9] (32Hz, F <sub>SLOW</sub> /1024)               | RT[13]              |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 101  | ST Interrupt = RT[8] (64Hz, F <sub>SLOW</sub> /512)                |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 110  | ST Interrupt = RT[7] (128Hz, F <sub>SLOW</sub> /256)               | 1                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         |       | 111  | ST Interrupt = RT[6] (256Hz, F <sub>SLOW</sub> /128)               |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [6]   | 1/0  | EXT Interrupt takes place at Rising/Falling edge                   | Rising              |       |                                                                         |                                                    |  |  |     |                                                      |  |

| \$15        | SLP  | W       | [7:0] |      | Write 0x5A to sleep                                                | XX                  |       |                                                                         |                                                    |  |  |     |                                                      |  |

| \$16        | WDGC | W       | [7:0] |      | Write 0xA5 to clear watchdog timer                                 | XX                  |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      | W       | [2]   | 0    | Write 0 to clear RTC counter (read as high)                        | x                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | [3]   | 1/0  | RTC Enable/Disable                                                 | Enable              |       |                                                                         |                                                    |  |  |     |                                                      |  |

| \$17        | OPMD |         |       | 000  | F <sub>FAST</sub> = F <sub>FAOS</sub> /1                           |                     |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      | R/W     | [6:4] | 001  | F <sub>FAST</sub> = F <sub>FAOS</sub> /2                           | F <sub>FAOS</sub> / |       |                                                                         |                                                    |  |  |     |                                                      |  |

|             |      |         | _     | 010  | FFAST = FFAOS/4                                                    | 1                   |       |                                                                         |                                                    |  |  |     |                                                      |  |

# 深圳市矽源特科技有限公司 ShenZhen ChipSourceTek Technology Co., Ltd.

| Addr.        | Name                | R/W                    | Bit   | Data     | Description NY8                                                         | Default                                  |       |

|--------------|---------------------|------------------------|-------|----------|-------------------------------------------------------------------------|------------------------------------------|-------|

|              |                     |                        |       | 011      | F <sub>FAST</sub> = F <sub>FAOS</sub> /8                                |                                          |       |

|              |                     |                        |       | 100      | FFAST = FFAOS/16                                                        |                                          |       |

|              |                     |                        |       | 101      | FFAST = FFAOS/32                                                        |                                          |       |

|              |                     |                        |       | 110      | F <sub>FAST</sub> = F <sub>FAOS</sub> /64                               | _                                        |       |

|              |                     |                        |       | 111      | FFAST = FFAOS/128                                                       | -                                        |       |

|              |                     |                        | [7]   | 1/0      | FCPU = FFAST/FSLOW (32KHz)                                              | FFAST                                    |       |

|              |                     |                        | [']   | 000      |                                                                         | I FAST                                   |       |

|              |                     |                        |       |          | Charge pump clock = $RT[6]$ (256Hz, $F_{SLOW}/128$ )                    | _                                        |       |

|              |                     |                        |       | 001      | Charge pump clock = RT[5] (512Hz, F <sub>SLOW</sub> /64)                | _                                        |       |

|              |                     |                        |       | 010      | Charge pump clock = RT[4] (1KHz, F <sub>SLOW</sub> /32)                 | _                                        |       |

|              |                     |                        | [2:0] | 011      | Charge pump clock = RT[3] (2KHz, F <sub>SLOW</sub> /16)                 | 32KHz                                    |       |

| \$1A         | LCDPC               | R/W                    | [2.0] | 100      | Charge pump clock = RT[2] (4KHz, F <sub>SLOW</sub> /8)                  | 021012                                   |       |

|              |                     |                        |       | 101      | Charge pump clock = RT[1] (8KHz, F <sub>SLOW</sub> /4)                  |                                          |       |

|              |                     |                        |       | 110      | Charge pump clock = RT[0] (16KHz, F <sub>SLOW</sub> /2)                 |                                          |       |

|              |                     |                        |       | 111      | Charge pump clock = 32KHz (FsLow)                                       | -                                        |       |

|              |                     |                        | [3]   | 1/0      | LCD Power (Rbias or C_Pump) Enable/ Disable                             | Enable                                   |       |

|              |                     |                        | [0]   | 100      | LCD clock = RT[6] (256Hz, FsLow/128)                                    |                                          |       |

|              |                     |                        |       |          | 100                                                                     | LCD clock = RT[5] (512Hz, FsLow/64)      |       |

|              |                     | CDC <sup>[2]</sup> R/W |       | [2:0]    |                                                                         |                                          | RT[6] |

|              |                     |                        |       |          | 110                                                                     | LCD clock = RT[4] (1KHz, $F_{SLOW}/32$ ) |       |

| \$1B         | LCDC <sup>[2]</sup> |                        |       | 111      | LCD clock = RT[3] (2KHz, F <sub>SLOW</sub> /16)                         |                                          |       |

| <b>•</b> • - |                     |                        |       | 00       | LCD OFF                                                                 | -                                        |       |

|              |                     |                        | [4:3] | 01       | LCD ON                                                                  | OFF                                      |       |

|              |                     |                        | [4.0] | 10       | LCD all '0'                                                             |                                          |       |

|              |                     |                        |       | 11       | LCD all '1'                                                             |                                          |       |

|              |                     |                        |       | 00       | LVD level = 1.05V or 1.75V*                                             |                                          |       |

|              |                     | R/W                    | [1:0] | 01       | LVD level = 1.15V or 1.85V*                                             | 00                                       |       |

| \$1C         | LVD                 | 17/14                  | [1.0] | 10       | LVD level = 1.25V or 1.95V*                                             | 00                                       |       |

| ψīσ          |                     |                        |       | 11       | LVD level = 1.3V or 2.0V*                                               |                                          |       |

|              |                     | R/W                    | [4]   | 1/0      | LVD Enable/Disable                                                      | Disable                                  |       |

| ¢20          |                     | R/W                    | [7]   | 1/0      | LVD status: VDD <lvd level="" vdd="">LVD level</lvd>                    | X                                        |       |

| \$29         | AUD                 | R/VV                   | [0]   | 1/0<br>0 | Buzzer output Enable/Disable<br>CH01 = CH0 + CH1; 2 channel buzzer      | Disable                                  |       |

|              |                     |                        | [4]   | 1        | CH01 = CH0 + CH0; 1 channel buzzer                                      | 0                                        |       |

| \$2B         | MIX                 | R/W                    |       | 0        | BZDT from CH01                                                          | -                                        |       |

|              |                     |                        | [5]   | 1        | BZDT from FT                                                            | 0                                        |       |

|              |                     |                        |       | 00       | RFC Disable                                                             |                                          |       |

|              |                     |                        |       | 01       | RFC output the reverse signal of CX from RR                             |                                          |       |