ShenZhen ChipSourceTek Technology Co., Ltd.

TR4P151/153

### TR4P151/153 General Purpose MCU

### 1. General Descriptions

The TR4P151/153 series are high-performance 4-bit RISC micro-controller embedded with up to 2KX12 bits OTP, 256X4 bits SRAM, one simple ADC, 8 bit PWM, up to 11 Input/Output ports and one input port. It's flexible and cost-effective solution for general purpose MCU applications.

#### 2. Features

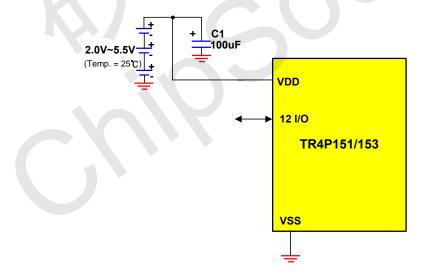

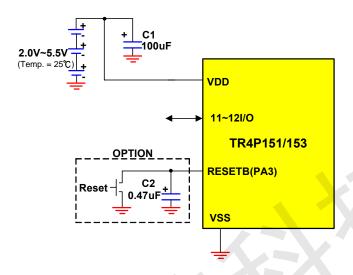

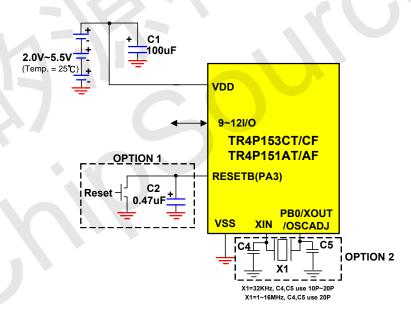

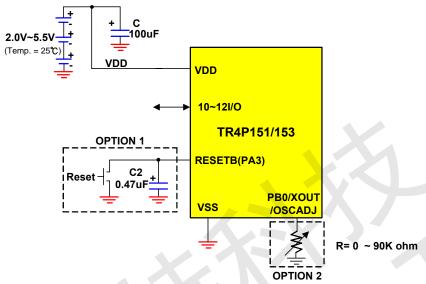

- Operating voltage: (1) 2.0V to 5.5V for Temp. = 25°C (2) 2.2V to 5.5V for Temp. = -40°C ~+85°C

- This MCU can operate in high speed and low speed mode by software. Below is the chip performance in different modes.

- (a) Internal high speed HRCOSC: 8 MIPS / 4 MIPS / 2 MIPS / 1 MIPS.

- (b) Internal low speed LRCOSC: 114.69KIPS / 57.34 KIPS / 28.67 KIPS / 14.33 KIPS. (KIPS means thousand instructions per second)

- (c) External EXTOSC: 8 MIPS (16 MHz X'tal) ~ 0.5 MIPS (1 MHz X'tal).TR4P151AT/AF only.

- Memory Size

- □ Program ROM size : 2KX12 bits (OTP type)

- □ SRAM size: total 256x4 bits SRAM

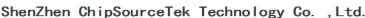

- Wake up function for power-down mode

- ☐ HALT mode wake up source: RTC timer overflow, PA0~3, PB0~3 and PD0~3 edge trigger

- 11 input /output ports: PA0~PA2, PB0~PB3, PD0~PD3. Each I/O can be bit programmable as input or output port. These 11 I/Os also provided level-change-wakeup function. Pull up and pull down resistor setting is available by software.

- 1 input port PA3, PA3 is shared with RSTB (reset) pin by option. It also provides level-change-wakeup function. Pull up and pull down resistor can be configured by software too.

- Port A, Port B and Port D are provided with high sink current 24mA @VDD=5V,Vol=0.5V( except PA3 )

- Port A, Port B and Port D are provided with high drive current 23mA @VDD=5V,Voh=4.5V( except PA3 )

- PA1 built-in 38KHz modulator by option.

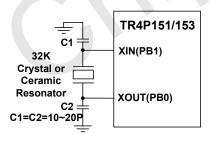

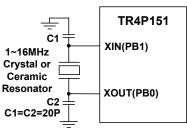

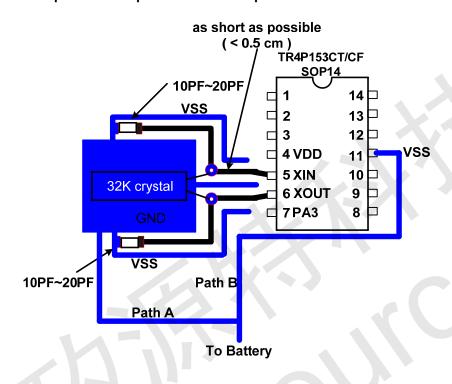

- Built-in external 32Kl or 1~16MHz X'tal oscillator by option.

- One 6 bit simple AD converter.

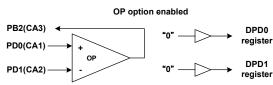

- One Op-Amp is provided, three pins shared with PD0, PD1, PB2 (by option).

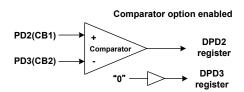

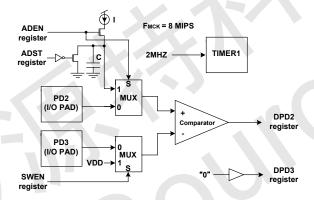

- One comparator is provided, two input pins shared with PD2, PD3 (by option).

- Three timers

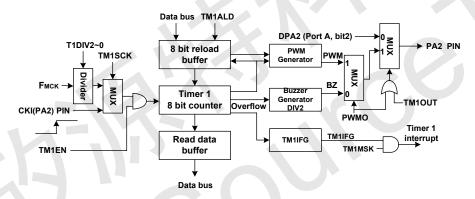

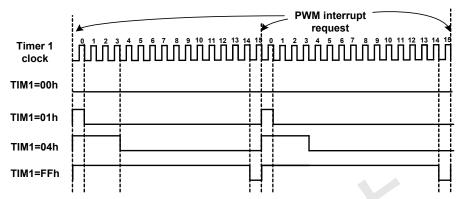

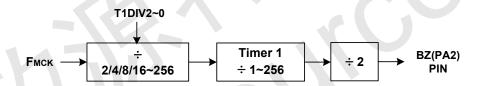

- ☐ Timer 1: 8 bits timer/counter/PWM, its clock source can be from chip-internal or external.

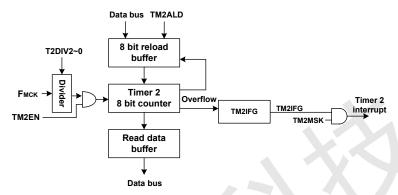

- ☐ Timer 2: 8 bits timer

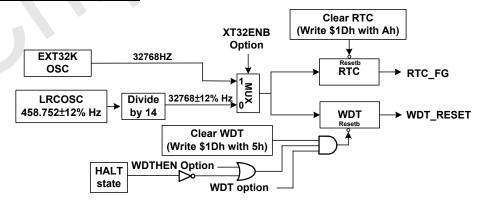

- ☐ RTC: time period 0.125 /0.25/0.5/1 Sec or 15.625/31.25/62.5/125 ms,

RTC Clock source comes from internal LRCOSC or external 32k X'tal oscillator.

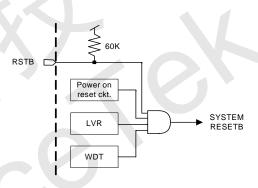

- Four reset condition

- □ Low voltage reset (LVR 1.8V)

- □ Power on reset

- ☐ External RSTB pin shared with PA3 pin by option.

- □ Watch dog timer overflow reset (0.125 sec ~ 1 sec by option)

- Three internal interrupt sources: TIMER1, TIMER2 or RTC interrupt.

- WDT(Watch dog timer)

- □ WDT can be enabled/disabled in HALT mode by option

- □ WDT clock source comes from internal LRCOSC or external 32K X'tal for reliable operation.

- Provides 8 Bits PWM, PWM signal output is shared with PA2 pin by option.

- Built-in high frequency internal 32MHz RC oscillator (HRCOSC, frequency deviation within ±2%, temperature range at -40℃~+85℃, Vdd = 2.0V to 5.5V)

- Built-in low frequency internal RC OSC (LRCOSC) 459KHz (frequency deviation within ±12%)

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

TR4P151/153

#### Selection table

| Feature<br>P/N          | OTP ROM                           | SRAM<br>(bits) | I/O Pin                                    | OP and<br>Comparator | Simple<br>ADC | User<br>Information<br>block<br>( Note1) | COB by |     |     | Support<br>FT test | Reset<br>Flag |

|-------------------------|-----------------------------------|----------------|--------------------------------------------|----------------------|---------------|------------------------------------------|--------|-----|-----|--------------------|---------------|

| TR4P151AT<br>(SOP8)     | 1.3K words<br>( 1280 + 16 words ) | 400.4          |                                            | No                   | No            | 16 words                                 | No     | Yes | Yes | Yes                | Yes           |

| TR4P151AF<br>(SOP8)     | 1.5K words<br>( 1504 words )      | 128x4          | 5 I/O + 1 I                                | No                   | No            | No                                       | Yes    | Yes | Yes | No                 | Yes           |

| TR4P153BT<br>(SOP8/14)  | 1.6K words<br>( 1536 + 48 words ) |                |                                            | 1 I ( no support     | No            | 48 words                                 | No     | No  | No  | Yes                | No            |

| TR4P153CT<br>(SOP14)    | 1.6K words<br>( 1536 + 48 words ) | <b></b> 4      | 11 I/O + 1 I<br>( 5 I/O + 1 I<br>for SOP8) |                      | Yes           | 48 words                                 | No     | Yes | No  | Yes                | No            |

| TR4P153CF<br>(SOP8/14)  | 2K words<br>( 1984 words)         | 256x4          | 4                                          |                      | No            | No                                       | Yes    | Yes | No  | No                 | No            |

| TR4P153DAI<br>(SOT23-6) | 2K words<br>( 1984 words)         |                | 3I/O+1 I                                   | No                   | No            | No                                       | No     | No  | No  | No                 | No            |

Note 1: Support user Information block (48X12 bits) for serial number, lot number or user optional codes ...etc. It's located at address 640h ~ 66Fh.

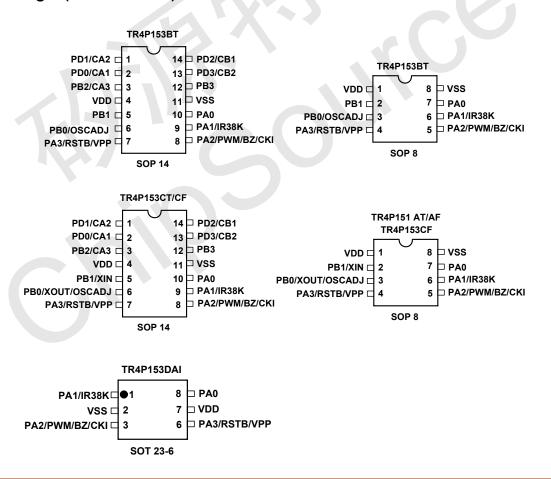

### **Package (6/8/14 SOP)**

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

E-mail: Sales@ChipSourceTek.com

Tony.Wang@ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

TR4P151/153

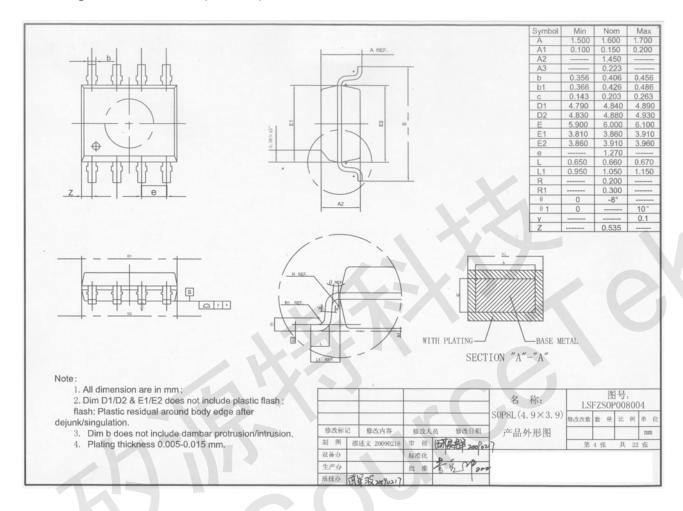

### Package Dimension(8SOP)

ShenZhen ChipSourceTek Technology Co. , Ltd.

TR4P151/153

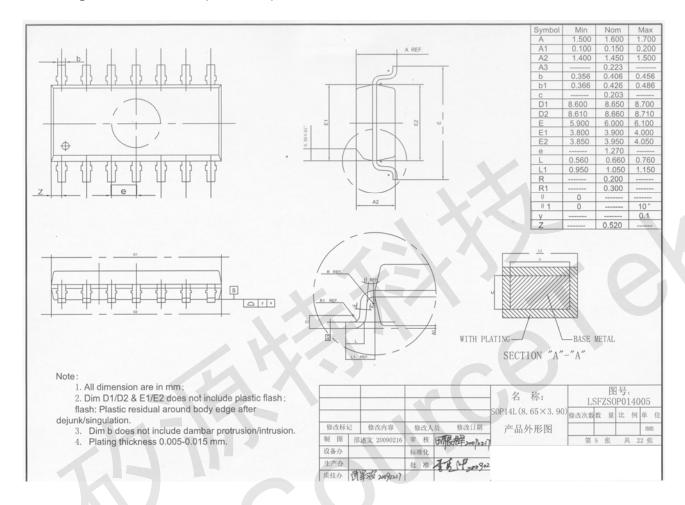

### Package Dimension(14SOP)

ShenZhen ChipSourceTek Technology Co. , Ltd.

TR4P151/153

#### 3. Pads Information

| PAD Name          | Туре | State<br>After<br>Reset | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Input       | •    | •                       |                                                                                                                                                                                                                                                                                                                                                                              |

| VDD               | I    | High                    | Power input pin                                                                                                                                                                                                                                                                                                                                                              |

| VSS               | I    | Low                     | Ground input pin                                                                                                                                                                                                                                                                                                                                                             |

| General I/O p     | orts |                         |                                                                                                                                                                                                                                                                                                                                                                              |

| PA0~PA2           | I/O  | XXX                     | PA0~PA2 are programmable I/O ports, with pull up and down resistor 100K ohm. Level-change-wakeup function is provided. PA1 is shared with IR38K function by option. PA2 is shared with PWM/CKI/BZ functions by option.                                                                                                                                                       |

| PA3<br>(RSTB/VPP) | I    | Х                       | PA3 is an input pin only, with pull up resistor 60K ohm, or pull down resistor 100K ohm.  Level-change-wakeup function is provided.  PA3 is shared with RSTB pin by option.                                                                                                                                                                                                  |

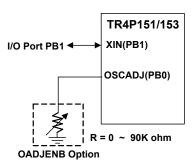

| PB0~PB3           | I/O  | XXXX                    | PB0~PB3 are programmable I/O ports, with pull up and down resistor 100K ohm. Level-change-wakeup function is provided. PB0 is shared with XOUT/OSCADJ by option. OSCADJ pin is used for frequency adjust of HRCOSC. PB1 is shared with XIN pin by option. XIN and XOUT is connected to external 32K or 1~16MHz X'tal. PB2 is shared with the output CA3 of Op Amp by option. |

| PD0~PD3           | I/O  | XXXX                    | Port D is a programmable I/O port, with pull up and down resistor 100K ohm.  Level-change-wakeup function is provided.  PD0 and PD1 are shared with two inputs (CA1, CA2) of Op AMP by option.  PD2 and PD3 are shared with two inputs (CB1, CB2) of a comparator by option. CB2 pin is also analog input of Simple ADC by option.                                           |

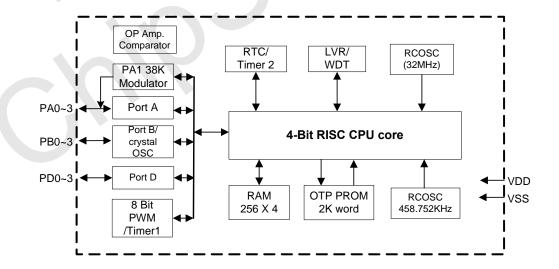

### **Block Diagram**

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

E-mail: Sales@ChipSourceTek.com Tony.Wang@ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

TR4P151/153

### 4. ELECTRICAL CHARACTERISTICS

### 4.1 Absolute Maximum Ratings

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYSMBOL          | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| DC Supply Voltage     | V+               | < 7.0           | V    |

| Input Voltage Range   | V <sub>IN</sub>  | -0.5 to VDD+0.5 | V    |

| Operating Temperature | T <sub>A</sub>   | -40 to +85      | °C   |

| Storage Temperature   | T <sub>STO</sub> | -50 to +150     | °C   |

### 4.2 DC/AC Characteristics

### DC CHARACTERISTICS (TA = 25°C, VDD = 3V, unless otherwise noted)

| PARAMETER                      | SYMBOL             | TEST CONDITIONS                                          |                     | LIMIT                      |                     | UNIT  |

|--------------------------------|--------------------|----------------------------------------------------------|---------------------|----------------------------|---------------------|-------|

| PARAMETER                      | STWIDOL            | TEST CONDITIONS                                          | Min                 | Тур                        | Max                 | ONIT  |

|                                | $V_{VDD1}$         | Temp. = 25°C                                             | 2.0                 | -                          | 5.5                 | V     |

| Operating voltage              | $V_{VDD2}$         | Temp.= -40°C ~+85°C                                      | 2.2                 |                            | 5.5                 | V     |

|                                | I <sub>OP1</sub>   | VDD=3V , MCU run 8 MIPS                                  |                     | 2.6                        |                     | mA    |

|                                | I <sub>OP2</sub>   | VDD=5V , MCU run 8 MIPS                                  |                     | 3.0                        |                     | mA    |

| Operating Current              | I <sub>OP3</sub>   | VDD=3V , MCU run 1 MIPS                                  |                     | 1.6                        | 1                   | mA    |

| Operating Current              | I <sub>OP4</sub>   | VDD=5V , MCU run 1 MIPS                                  |                     | 2.0                        |                     | mA    |

|                                | I <sub>OP5</sub>   | VDD=3V , MCU run 14 KIPS                                 |                     | 50                         |                     | uA    |

|                                | I <sub>OP6</sub>   | VDD=3V, MCU run 114.7 KIPS                               |                     | 200                        |                     | uA    |

|                                | I <sub>STBY1</sub> | MCU stop in HALT mode WDT & RTC off                      | 77                  | 2.5 (VDD=3V)<br>3 (VDD=5V) |                     | uA    |

| Standby Current                | I <sub>STBY2</sub> | 1.VDD=5V<br>2.MCU stop in HALT mode,<br>WDT on or RTC on |                     | 8                          |                     | uA    |

| Input High Level               | V <sub>IH</sub>    | All I/O port                                             | 0.8*V <sub>DD</sub> |                            |                     | V     |

| Input Low Level                | V <sub>IL</sub>    | All I/O port                                             |                     |                            | 0.2*V <sub>DD</sub> | V     |

| O. 4 4 D.: O4                  | I <sub>OH1</sub>   | VDD=3V , V <sub>OH</sub> =2.5V,All I/O port              | -8                  | -15                        |                     | mA    |

| Output Drive Current           | I <sub>OH2</sub>   | VDD=5V , V <sub>OH</sub> =4.5V,All I/O port              | -12                 | -23                        |                     | mA    |

|                                | I <sub>OL1</sub>   | VDD=3V , V <sub>OL</sub> =0.5V,All I/O port              | 8                   | 15                         |                     | mA    |

| Output Sink Current            | I <sub>OL2</sub>   | VDD=5V , V <sub>OL</sub> =0.5V,All I/O port              | 12                  | 24                         |                     | mA    |

| PA,PB,PD pull down             | R <sub>down1</sub> | Pull down 180K ohm, VDD=3V                               | 140                 | 180                        | 220                 | K ohm |

| Res.                           | R <sub>down2</sub> | Pull down 100K ohm, VDD=5V                               | 60                  | 90                         | 120                 | K ohm |

| PA,PB,PD pull up Res.          | R <sub>up1</sub>   | Pull up 180K ohm, VDD=3V                                 | 140                 | 180                        | 220                 | K ohm |

| ( except PA3 )                 | R <sub>up2</sub>   | Pull up 100K ohm, VDD=5V                                 | 60                  | 90                         | 120                 | K ohm |

| PA3 pull up Res.               | R <sub>up3</sub>   | Pull up 60K ohm ,VDD=2V~5V                               | 40                  | 60                         | 80                  | K ohm |

| LVR                            | V <sub>LVR1</sub>  | Temp. = 25°C                                             | 1.6                 | 1.8                        | 2.0                 | V     |

|                                | $V_{LVR2}$         | Temp.= -40°C~+85°C                                       | 1.4                 | 1.8                        | 2.2                 | V     |

| SRAM Data<br>Retention voltage | $V_{DR}$           |                                                          | 1.0                 |                            |                     | V     |

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

TR4P151/153

### AC CHARACTERISTICS (TA = 25°C, VDD = 3V, unless otherwise noted)

| PARAMETER                                                                                 | SYMBOL               | - TEST CONDITIONS                                                                                                                           |       | LIMIT                                                                                                             |       |      |  |

|-------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------|-------|------|--|

| FARAIVIETER                                                                               | 3 I WIBOL            | TEST CONDITIONS                                                                                                                             | Min   | Тур                                                                                                               | Max   | UNIT |  |

| Internal HRCOSC Frequency                                                                 | F <sub>HRCOSC</sub>  | VDD = 2.0V~5.5V<br>Temp = -40°C ~+85°C                                                                                                      | 31.36 | 32 ±2%                                                                                                            | 32.64 | MHz  |  |

| Internal LRCOSC Frequency                                                                 | F <sub>LRCOSC1</sub> | VDD = 2.0V~5.5V<br>Temp. = 25°C                                                                                                             |       | 458.752 ±12%                                                                                                      |       | KHz  |  |

|                                                                                           | F <sub>LRCOSC2</sub> | VDD = 2.0V~5.5V<br>Temp = -40°C ~+85°C                                                                                                      |       | 458.752 ±20%                                                                                                      |       | KHz  |  |

| External X'tal EXT32K                                                                     | F <sub>XT32K</sub>   | VDD = 2.0V~5.5V                                                                                                                             |       | 32768                                                                                                             |       | Hz   |  |

| External X'tal EXTOSC<br>( TR4P151AT/AF only )                                            | F <sub>XTOSC</sub>   | VDD = 2.0V~5.5V                                                                                                                             |       | 1~16                                                                                                              |       | MHz  |  |

| MCU operating frequency (clock source from FHRCOSC)                                       | F <sub>MCk1</sub>    | 1.in NORMAL mode<br>2.Clock source : F <sub>HRCOSC</sub><br>3.VDD = 2.0V~5.5V<br>4.Temp40°C ~+85°C                                          |       | 8 ±2%, 4 ±2%<br>2 ±2%, 1 ±2%<br>(Fhrcosc/4, Fhrcosc/8,<br>Fhrcosc/16, Fhrcosc/32)                                 |       | MIPS |  |

| MCU operating frequency ( clock source F <sub>LRCOSC</sub> )                              | F <sub>MCk2</sub>    | 1.in GREEN mode<br>2.VDD = 2.0V~5.5V<br>3.Temp. = 25°C                                                                                      |       | 114.69±12%,57.34±12%<br>28.67±12%,14.33±12%                                                                       |       | KIPS |  |

| MCU operating frequency<br>(clock source from F <sub>XTOSC</sub> )<br>(TR4P151AT/AF only) | F <sub>мскз</sub>    | 1.in NORMAL mode<br>2.Clock source : $F_{XTOSC}$<br>3.VDD = 2.0V~5.5V<br>4 Temp40 $^{\circ}$ C~+85 $^{\circ}$ C<br>5.If $F_{XTOSC}$ = 16Mhz |       | 8 , 4, 2, 1<br>( F <sub>XTOSC</sub> /2, F <sub>XTOSC</sub> /4,<br>F <sub>XTOSC</sub> /8, F <sub>XTOSC</sub> /16 ) |       | MIPS |  |

| PA1, 38KHz output<br>( clock source F <sub>HRCOSC</sub> )                                 | F <sub>38K1</sub>    | 1.in NORMAL mode<br>2.PA1 IR38K option enabled<br>3.Register F38K=1<br>4.Temp. = 25°C                                                       |       | 38.09 ±2%<br>(F <sub>HRCOSC</sub> /840)                                                                           |       | KHz  |  |

| PA1, 38KHz output<br>( clock source F <sub>LRCOSC</sub> )                                 | F <sub>38K2</sub>    | 1.in GREEN mode<br>2.PA1 IR38K option enabled<br>3.Register F38K=1<br>4.Temp. = 25°C                                                        |       | 38.23 ±12%<br>(F <sub>LRCOSC</sub> /12)                                                                           |       | KHz  |  |

|                                                                                           | T <sub>RTC1</sub>    | VDD = 2.0V~5.5V<br>Temp. = 25°C<br>clock source F <sub>LRCOSC</sub><br>SPUP option enabled                                                  |       | 0.125±12%, 0.25±12%<br>0.5±12%, 1.0±12%                                                                           |       | Sec  |  |

| RTC period                                                                                | T <sub>RTC2</sub>    | VDD = 2.0V~5.5V<br>Temp. = 25℃<br>clock source F <sub>LRCOSC</sub><br>SPUP option disabled                                                  |       | 15.625±12%,31.25±12%<br>62.5±12%, 125±12%                                                                         |       | ms   |  |

|                                                                                           | Тктсз                | VDD = 2.0V~5.5V<br>clock source FxT32K<br>SPUP option enabled                                                                               |       | 0.125, 0.25, 0.5, 1.0                                                                                             |       | Sec  |  |

|                                                                                           | T <sub>RTC4</sub>    | VDD = 2.0V~5.5V<br>clock source FxT32K<br>SPUP option disabled                                                                              |       | 15.625, 31.25, 62.5, 125                                                                                          |       | ms   |  |

| WDT period                                                                                | T <sub>WDT1</sub>    | VDD = 2.0V~5.5V<br>Temp. = 25°C<br>clock source F <sub>LRCOSC</sub>                                                                         |       | 0.125±12%, 0.25±12%<br>0.5±12% , 1.0±12%                                                                          |       | Sec  |  |

|                                                                                           | TwdT2                | VDD = 2.0V~5.5V<br>clock source FxT32K                                                                                                      |       | 0.125, 0.25, 0.5, 1.0                                                                                             |       | Sec  |  |

ShenZhen ChipSourceTek Technology Co., Ltd.

TR4P151/153

| Stable clock delay after power on or system reset           | CKstable1 | System oscillatorHRCOSC ( Note 1 ) | 160us+ 1024 x (1/ Fмск1)<br>( Note 3 )     | us |

|-------------------------------------------------------------|-----------|------------------------------------|--------------------------------------------|----|

| (TR4P151AT/AF only)                                         |           | System oscillatorEXTOSC ( Note 2 ) | 160us<br>+ 1024 x (1/ Fмск2)<br>( Note 5 ) | us |

| Stable clock delay after wake up                            | CKstable3 | System oscillatorHRCOSC (Note 2)   | 64 x (1/ F <sub>MCK1</sub> )<br>( Note 3 ) | us |

| Stable clock delay<br>after wake up<br>(TR4P151AT/AF only ) | CKstable4 | System oscillatorEXTOSC ( Note 4 ) | 1024 x (1/ FMCK2)<br>( Note 5 )            | us |

Note1: The stable clock delay (CKstable1) is a delay between HRCOSC-started and 1st instruction-execution.

This delay will ensure stable system clock after power on or reset.

Note2: The stable clock delay (CKstable2) is a delay between clock output of EXTOSC and 1st instruction. This delay will ensure stable system clock after power on or reset.

Note3: The stable clock delay (CKstable3) is a delay between HRCOSC-started and 1st instruction-execution of wakeup. This delay will ensure stable system clock after wake up.

Note4: The stable clock delay (CKstable4) is a delay between EXTOSC-started and 1st instruction-execution of wakeup. This delay will ensure stable system clock after wake up.

Note5: FMCK1 and FMCK2 are MCU operating clock.

### AC Characteristics of OP ( $TA = 25^{\circ}C$ , VDD = $2V\sim5.5V$ , unless otherwise noted )

| PARAMETER             | SYMBOL            | SYMBOL TEST CONDITIONS |      | UNIT |         |      |

|-----------------------|-------------------|------------------------|------|------|---------|------|

| FAINAIVILILIX         | OTHIBOL           | TEST CONDITIONS        | Min  | Тур  | Max     | ONIT |

| Quiescent current     | I <sub>QUI</sub>  | VDD = 2V~5.5V          | 30   | 50   | 70      | uA   |

| Input voltage range   | V <sub>IN</sub>   |                        | 0    |      | VDD     | V    |

| Output voltage range  | V <sub>OUT</sub>  |                        | 0.1  |      | VDD-0.1 | V    |

| Offset voltage        | Vos               |                        | 10   |      | 100     | mV   |

| Output sink current   | I <sub>SINK</sub> |                        | 15   |      | 30      | uA   |

| Output source current | I <sub>sou</sub>  |                        | 150  |      | 300     | uA   |

| Output resistor load  | R <sub>L</sub>    |                        | 100K |      |         | Ohm  |

### AC Characteristics of Comparator ( TA = $25^{\circ}$ C, VDD = $2V\sim5.5V$ , unless otherwise noted )

| PARAMETER           |         | SYMBOL           | SYMBOL TEST CONDITIONS |     | LIMIT |     |      |  |

|---------------------|---------|------------------|------------------------|-----|-------|-----|------|--|

| TANAMETER           | OTHIBOE |                  | 1201 GONDITIONS        | Min | Тур   | Max | UNIT |  |

| Quiescent current   |         | I <sub>QUI</sub> | VDD = 2V~5.5V          | 1   |       | 2   | uA   |  |

| Input voltage range |         | V <sub>IN</sub>  |                        | 0   |       | VDD | V    |  |

| Offset voltage      |         | Vos              |                        | 10  |       | 100 | mV   |  |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

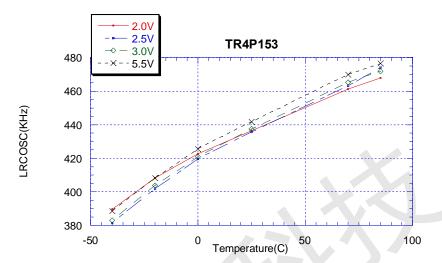

The LRCOSC frequency VS. temperature, VDD=2.0V~5.5V

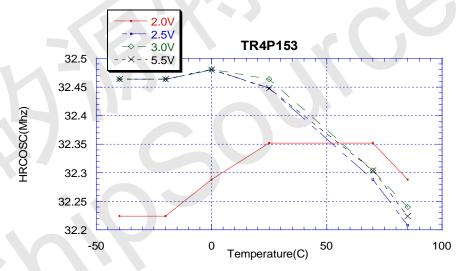

The HRCOSC frequency VS. temperature, VDD=2.0V~5.5V

ShenZhen ChipSourceTek Technology Co., Ltd.

TR4P151/153

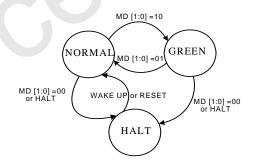

#### 5. FUNCTIONAL DESCRIPTION

This MCU inside TR4P151/153 series are high performance processor. The operation speed can be range from 0.5 MIPS to 8 MIPS depending on different applications.

#### 5.1 Program ROM (OTP ROM)

#### TR4P153B/C series

TR4P153XX series support two kind of OTP ROM arrangement. They are TR4P153BT ,TR4P153CT, TR4P153CF and TR4P153DA-S6. The OTP ROM memory plan is shown below:

| Address     | TR4P153BT<br>(1.6 K OTP ROM)   | TR4P153CT<br>(1.6 K OTP ROM)   | TR4P153CF<br>TR4P153DA-S6<br>( 2 K OTP ROM ) |

|-------------|--------------------------------|--------------------------------|----------------------------------------------|

| 000h ~ 0FFh |                                |                                |                                              |

| 100h ~ 1FFh | User area 1.5K                 | User area 1.5K                 | User area 1.5K                               |

| 200h ~ 2FFh | ( 1536 X12 )                   | ( 1536 X12 )                   | ( 1536 X12 )                                 |

|             |                                | / <b>-</b>   /                 |                                              |

| 500h ~ 5FFh |                                |                                |                                              |

| 600h ~ 63Fh | Reserved area                  | Reserved area                  | Reserved area                                |

| 640h ~ 66Fh | User Information block(48X12). | User Information block(48X12). |                                              |

|             | For data store only, can't be  | For data store only, can't be  | User area 0.5K                               |

|             | used to store program.         | used to store program.         | ( 448X12 )                                   |

| 670h ~ 671h | _                              | Simple ADC calibration data    |                                              |

| 672h ~ 7FFh | Reserved area                  | Reserved area                  |                                              |

- Note: 1. For TR4P153XX series, the content of OTP ROM address \$640h~\$66Fh can be read by program. Address \$600h~\$63Fh and \$672h~\$7FFh can't be read by program.

- 2. To read registers DMDL, DMDM and DMDH, only LD A,(n) instruction can be used. Other instructions are not allowed. (n= DMDL, DMDM or DMDH

- 3. If DMA2~DMA0 pointed address is located at invalid address 600h~61Fh or 700h~7FFh, DMA2.2, DMA2.1, DMA2.0 will be regarded as 0 by hardware automatically, DMA0 and DMA1 will not be affected.

- 4. The simple ADC is only applied on TR4P153CT.

TR4P153BT/CT support 1.6 K words user ROM which is located on \$000h  $\sim$  \$5FFh, \$640h  $\sim$  \$66Fh and \$670h $\sim$ \$671h. The first user area \$000h  $\sim$  \$5FFh stores user program area. The second user area \$640h  $\sim$  \$66Fh that named user information block stores serial number, lot number or user optional codes...etc. The third user area \$670h $\sim$ \$671h stores Simple ADC calibration data. In addition to the above points, there are still the reserved areas. They are located at \$600h  $\sim$  \$63Fh and \$672h  $\sim$  \$7FFh, they can't be read by software.

TR4P153CF/DA supports 2 K words OTP ROM which is located on \$000h ~ \$5FFh and \$640h ~ \$7FFh. These two areas store user program. Although \$640h~\$7FFh is user area, but data in \$672h~\$7FFh can't be read by software. The reserved area, \$600h ~ \$63Fh, can't be read by program also.

To read OTP ROM data, use DMA2~DMA0 registers as address pointer. The address range is located in \$000h ~ \$5FFh and \$640h~\$671h. After these registers (DMA0~2) are specified by software, the 12bits data of ROM can be moved to A register by three instructions, they are "LD A, (DMDL)", "LD A, (DMDM)" and "LD A, (DMDH)". The three instructions mentioned above are two cycle instruction, all others instructions are single cycle instruction.

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

TR4P151/153

#### TR4P151A series

TR4P151A series support two kind of OTP ROM arrangement. They are TR4P151AT and TR4P151AF. The OTP ROM memory plan is shown below:

| Address     | TR4P151AT ( 1.3 K OTP ROM )                 | TR4P151AF ( 1.5 K OTP ROM )    |

|-------------|---------------------------------------------|--------------------------------|

| 000h ~ 0FFh |                                             |                                |

| 100h ~ 1FFh | User area 1.3K                              |                                |

| 200h ~ 2FFh | ( 1280 X 12 )                               |                                |

| 300h ~ 3FFh | ]                                           | User area 1.5K                 |

| 400h ~ 4FFh |                                             | ( 1504 X 12 )                  |

| 500h ~ 50Fh | User Information block (16X12). For data    |                                |

|             | store only, can't be used to store program. |                                |

| 510h ~ 5CDh | Reserved area                               |                                |

| 5CEh~5CFh   |                                             | Serial number area ( 2 words ) |

| 5D0h ~ 5FFh | Reserved area                               | Reserved area                  |

- Note: 1. To read registers DMDL, DMDM and DMDH, only LD A,(n) instruction can be used. Other instructions are not allowed. ( n= DMDL, DMDM or DMDH )

- 2. For TR4P151AT, the content of OTP ROM address \$500h~\$50Fh can be read by program. Address \$510h~\$5FFh can't be read by program.

- 3. If DMA2~DMA0 pointed address is located at invalid address \$5D0h~\$5FFh, DMA2.2, DMA2.1, DMA2.0 will be regarded as 0 by hardware automatically, DMA0 and DMA1 will not be affected.

| Symbol | Addr | R/W | Reset | D3     | D2     | D1     | D0     | Description                                                                                                                                                                                                                                        |

|--------|------|-----|-------|--------|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA0   | 18H  | R/W | XXXX  | DMA0.3 | DMA0.2 | DMA0.1 | DMA0.0 | DMA0~DMA2(exclude DMA2.3) build a 11                                                                                                                                                                                                               |

| DMA1   | 19H  | R/W | XXXX  | DMA1.3 | DMA1.2 | DMA1.1 | DMA1.0 | bit addressing space for read ROM data.                                                                                                                                                                                                            |

| DMA2   | 1AH  | R/W | xxxx  | DMA2.3 | DMA2.2 | DMA2.1 | DMA2.0 | DMA0 is the lowest nibble address,DMA2 is the highest nibble address. DMA2.3: It's a user usable register only, it's useless for address setting.                                                                                                  |

| DMDL   | 1CH  | R   | xxxx  | DMDL.3 | DMDL.2 | DMDL.1 | DMDL.0 | DMDL is used to read low nibble data from ROM that addressed by DMA0 ~ DMA2.                                                                                                                                                                       |

| DMDM   | 1DH  | R/W | xxxx  | DMDM.3 | DMDM.2 | DMDM.1 | DMDM.0 | <ol> <li>DMDM is used to read middle nibble data from ROM that addressed by DMA0 ~ DMA2.</li> <li>Write this register with data 05h will clear watch dog timer (WDT)</li> <li>Write this register with data 0Ah will clear RTC counter.</li> </ol> |

| DMDH   | 1EH  | R   | xxxx  | DMDH.3 | DMDH.2 | DMDH.1 | DMDH.0 | DMDH is used to read high nibble data from ROM that addressed by DMA0 ~ DMA2.                                                                                                                                                                      |

For example, assume the data of address 356H is 587H.

LD A, #3

LD (DMA2), A

LD A, #5

LD (DMA1), A

LD À, #6

LD (DMA0), A ; ROM address = 356H

LD A, (DMDL) ; A register = 7H; low nibble data of ROM address 356H LD A, (DMDM) ; A register = 8H; middle nibble data of ROM address 356H LD A, (DMDH) ; A register = 5H; high nibble data of ROM address 356H

. . . . . . .

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

TR4P151/153

### 5.2 SRAM and I/O Memory Map

TR4P151/153 series are provided 256 nibbles SRAM. SRAM is separated into 8 pages (MAH0~7). Every page has 32 nibbles (with same address, \$20H~\$3FH). This addressing space of SRAM is different from ROM's address.

| INDIVI 3 address.           |               |                   |                                                             |

|-----------------------------|---------------|-------------------|-------------------------------------------------------------|

| Direct Addressi             | ng (use MAH ) | Real SRAM Address | SRAM MAP                                                    |

| MAH=XH<br>( MAH no effect ) | 00H~1FH       |                   | Common I/O port and SFR(special function register) register |

| MAH=0H                      | 20H~3FH       | 00H~1FH           |                                                             |

| MAH=1H                      | 20H~3FH       | 20H~3FH           |                                                             |

|                             |               |                   | USER SRAM (256x4)                                           |

| MAH=6H                      | 20H~3FH       | C0H~DFH           |                                                             |

| MAH=7H                      | 20H~3FH       | E0H~FFH           |                                                             |

The addressing space is separated into several pages. Software can select working pages by setting MAH register. Each page contains two blocks and each block contains 32 nibbles. The lower block (00H ~ 1FH) is used for IO registers and special registers, it's named "common I/O block". This block will not affected by MAH setting. In any MAH setting, software can access register of this block directly. The higher block (20H~3FH) is used for user SRAM access. MAH register determines current access page of SRAM. The 20H~3FH address(in instructions) determines 32 nibble address in the current page.

The working space as shown below:

High 32 nibbles address space (20 ~ 3F H), MAH pointed SRAM space

Low 32 nibbles address space (0 ~ 1F H), I/O and special register, "common I/O block", MAH has no effect on this block

MAH = 0 selects 1st 32 nibbles SRAM

MAH = 1 selects 2nd 32 nibbles SRAM

MAH = 2 selects 3rd 32 nibbles SRAM

etc

MAH can be written by a special instruction "LDMAH" with direct data.

MAH can not be read by MCU. When interrupt happened, MAH data will be stored by hardware and restored by "RETI" command.

### 5.3 I/O Memory Map

The I/O memory map consists of common I/O, control registers and extended I/O space. Detailed operations are as follows.

#### 5.4 Common I/O and control register

The "common IO block" contains 32 address. All registers in this block can be accessed directly by these instructions: LD/ADC/SBC/OR/AND/XOR/INC/DEC/RLC/RRC/CMP/ADR. SET, CLR (bit set/clear) can only operate on the address range from 00H to 0FH.

Read common I/O instruction: LD/ADC/SBC/CMP/OR/AND/XOR (Ex. LD A,(n))

Write data to common I/O instruction: LD (n),A

Read and write common I/O instruction : DEC/INC/ADR/RRC/RLC ( Ex. DEC (n) )

U: unchanged X: unknown value R/W: readable & writeable R: readable only W: writeable only

| Symbol | Addr | R/W | Reset | D3     | D2     | D1 | D0 | Description               |

|--------|------|-----|-------|--------|--------|----|----|---------------------------|

| STATUS | 00H  | R/W | 00xx  | TM2IFG | TM1IFG | CF | ZF | ZF : Zero status register |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

TR4P151/153

|         |     |     |      |                        |         |         |         | CF: Carry status register TM1IFG: Timer 1 interrupt flag 0: no Timer1 interrupt occurred. 1: Timer1 interrupt occurred, it can be cleared by software. TM2IFG: Timer 2 interrupt flag 0: no Timer 2 interrupt occurred. 1: Timer2 interrupt occurred, it can be cleared by software.                                                                                                                                           |

|---------|-----|-----|------|------------------------|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     |     |      |                        |         |         |         | RTC will cause an interrupt (\$008h) when in NORMAL mode or GREEN mode. In HALT mode, RTC can wakeup MCU and program will go to wake up vector (\$004h). RTCS1, RTCS0: RTC interrupt period detailed description in Real Time Clock Interrupt section.                                                                                                                                                                         |

| RTC     | 01H | R/W | 0000 | RTCFG                  | F38K    | RTCS1   | RTCS0   | F38K is valid only when IREN is enabled. F38K = 1, PA1 output 38k clock F38K = 0, PA1 PIN 38K output signal disabled. PA1 keeps low if (option) IRNOR0 disabled. PA1 keeps high when IRNOR0 enabled.                                                                                                                                                                                                                           |

|         |     |     |      |                        |         | X       |         | RTCFG: RTC overflow flag 0: RTC overflow not occurred. 1: RTC overflow occurred, it can be cleared by software.                                                                                                                                                                                                                                                                                                                |

| IOC_PA  | 02H | R/W | 0000 | X                      | IOCA2   | IOCA1   | IOCA0   | Port PA0~PA2 input/output direction: 1: set port as output port individually 0: set port as input port individually PA3 is input only.                                                                                                                                                                                                                                                                                         |

| DATA_PA | 03H | R/W | xxxx | DPA3<br>(Read<br>only) | DPA2    | DPA1    | DPA0    | Read data from PA0~PA3 PIN or write data to PA0~PA2 PIN ( I/O direction is selected by IOC_PA register)                                                                                                                                                                                                                                                                                                                        |

| ADC     | 04H | R/W | 0000 | USER0                  | CASW    | ADEN    | ADST    | Simple ADC control register                                                                                                                                                                                                                                                                                                                                                                                                    |

| IOC_PB  | 05H | R/W | 0000 | IOCB3                  | IOCB2   | IOCB1   | IOCB0   | Port PB0~PB3 input/output direction : 1: set port as output port individually 0: set port as input port individually                                                                                                                                                                                                                                                                                                           |

| DATA_PB | 06H | R/W | xxxx | DPB3                   | DPB2    | DPB1    | DPB0    | Read data from PB0~PB3 port or write data to PB0~PB3 ( I/O direction is defined by IOC_PB register)                                                                                                                                                                                                                                                                                                                            |

| USER1   | 07H | R/W | XXXX | USER1.3                | USER1.2 | USER1.1 | USER1.0 | General purpose user RAM                                                                                                                                                                                                                                                                                                                                                                                                       |

| TMCTL   | 08H | R/W | 0000 | TM2EN                  | TM1EN   | TM1SCK  |         | TM1ALD: Timer 1 auto load control 0: Timer 1 auto load function turned off 1: Timer 1 auto load function turned on TM1SCK:Timer1 clock source selection 0: internal clock (frequency selected by SCALER1 register) 1: external clock (from PA2 pin) IOCA2 must be set to 0. TM1EN: Timer 1 enable control bit 0: Timer 1 disabled 1: Timer 1 enabled TM2EN: Timer 2 enable control bit 0: Timer 2 disabled 1: Timer 2 disabled |

ShenZhen ChipSourceTek Technology Co. ,Ltd.

TR4P151/153

| and TM2MSK will be cleared by HAL- instruction PWMO: PWM signal output to PA2 pin 0: PA2 pin is I/O pin 1: PA2 pin is I/O pin 1: PA2 pin is PWM output pin (The frequency of PWM is controlled by TM110UT and TM1ALD if PWMO=1) ENINT: Global interrupt enabled 1: global interrupt enabled 1: global interrupt maskled (FINIT) control the interrupt maskled (Timer1 interrupt disabled). 1: Timer 1 interrupt masked (Timer1 interrupt disabled). 1: Timer 2 interrupt masked (Timer1 interrupt disabled). 1: Timer 2 interrupt masked (Timer2 interrupt disabled). 1: Timer 2 int | SYS0    | 09H   | R/W   | 0000 | TM2MSK      | TM1MSK     | ENINT      | PWMO        | Notice: The PWMO, ENINT, TM1MSK         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|------|-------------|------------|------------|-------------|-----------------------------------------|

| PWMO: PWM signal output to PA2 pin 0 : PA2 pin is I/O pin 1 : PA2 pin is PWM output pin (The frequency of PWM is controlled by TMMOUT and TM1ALD if PWMO=1) : ENINT: Global interrupt enabled 0 : global interrupt enabled 0 : global interrupt enabled of Time 1 : Timer 1 interrupt masked (Filmer1 interrupt masked (Timer2 interrupt masked (Timer1 interrupt enabled).  1 : Timer 1 interrupt unmasked (Timer1 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt masked (Timer2 interrupt enabled).  1 : Timer 2 interrupt |         |       |       |      |             |            |            |             | and TM2MSK will be cleared by HALT      |

| O : PA2 pin is I/O pin   1 : PA2 pin is I/O pin   1 : PA2 pin is I/O pin   1 : PA2 pin is PWM output pin   (The frequency of PWM is controlled by TM10UT and TM1ALD if PWMO=1) ENINT: Global interrupt chabled   ENINT Control the interrupt disabled   1 : global interrupt disabled   1 : global interrupt enabled of Time   1, Timer 2 and RTC   TM1MSK : Timer 1 interrupt masked (Timer1 interrupt disabled).   1 : Timer 1 interrupt masked (Timer1 interrupt disabled).   1 : Timer 1 interrupt masked (Timer2 interrupt disabled).   1 : Timer 2 interrupt masked (Timer2 interrupt disabled).   1 : Timer 2 interrupt masked (Timer2 interrupt disabled).   1 : Timer 2 interrupt masked (Timer2 interrupt disabled).   1 : Timer 2 interrupt masked (Timer2 interrupt disabled).   1 : Timer 2 interrupt masked (Timer2 interrupt disabled).   2 : Timer2 interrupt masked (Timer2 interrupt disabled).   2 : Timer2 interrupt masked (Timer2 interrupt disabled).   2 : Timer2 interrupt masked (Timer2 interrupt disabled).   3 : Timer2 interrupt masked (Timer2 interrupt masked (Timer2 interrupt disabled).   4 : Timer2 interrupt masked (Timer2 interrupt disabled).   1 : Timer2 interrupt masked (Timer2 interrupt masked (Timer2 interrupt masked (Timer2 interrupt disabled).   1 : Timer2 interrupt masked (Timer2 interrupt masked (   |         |       |       |      |             |            |            |             | instruction                             |

| 1 : PA2 pin is PWM output pin (The frequency of PWM is controlled by TM10UT and TM1ALD if PWM0=1) ENINT: Global interrupt enabled 0 : global interrupt enabled 0 : global interrupt enabled, (ENINT control the interrupt enabled, (ENINT control the interrupt masked (Timer 1, Timer 2 and RTC) TM1MSK : Timer 1 interrupt masked (Timer 1 interrupt disabled).  1 : Timer 1 interrupt masked (Timer 1 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt masked (Timer 2 interrupt disabled).  1 : Timer 2 interrupt masked (Timer 2 interrupt masked (T   |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 TIM1.2 (TIM1.5) (TIM1.4) (TIM1.4) (TIM1.7) (TIM1.7) (TIM1.7) (TIM1.7) (TIM1.6) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 TIM1.2 (TIM1.5) (TIM1.5) (TIM1.5) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.8) DPD 0DH R/W 0000 IOCD3 IOCD2 IOCD1 IOCD1 IOCD0 Read port D data from Pt0-P53 port of write task input port individually DATA_PD 0DH R/W xxxx DPD3 DPD2 DPD1 IDPD0 Read port D data from Pt0-P53 port of write data from Pt0-P53 port of more of the fired port of defined by IOC_PD gilled interrupt control interrupt disabled.  1: global interrupt enabled, (ENINT control the interrupt mask of timer 1 interrupt mask of timer 1 interrupt disabled).  1: Timer 1 interrupt masked (Timer1 interrupt disabled).  1: Timer 2 interrupt masked (Timer2 interrupt disabled).  1: Timer 2 interrupt masked (Timer2 interrupt enabled).  TIM1.7 TIM1.0 S bit TIMER 1 counter (TIM1.5) (TIM1.5) (TIM1.5) (TIM1.4) (TIM1.7) (TIM1.6) (TIM1.4) (TIM1.7) (TIM2.7) (TIM2.7) (TIM2.8) (TIM2.8) (TIM2.8) (TIM2.8) (TIM2.8) (TIM2.9) (T |         |       |       |      |             |            |            |             |                                         |

| ENINT: Global interrupt enable 0: global interrupt enable 1: global interrupt enabled, (ENINT control the interrupt enabled, (ENINT control the interrupt enabled, (ENINT control the interrupt enabled of Time 1, Timer 2 and RTC)   TIMMSK: Timer 1 interrupt masked (Timer1 interrupt disabled). 1: Timer 4 interrupt unmasked (Timer1 interrupt enabled). TIM2MSK: Timer 2 interrupt masked (Timer2 interrupt enabled). 1: Timer 2 interrupt masked (Timer2 interrupt disabled). 1: Timer 2 interrupt masked (Timer2 interrupt enabled). 1: Timer 2 interrupt unmasked (Timer2 interrupt enabled). 1: Timer 2 interrupt enabled). 1: Tim   |         |       |       |      |             |            |            |             | ( The frequency of PWM is controlled by |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.5) (TIM1.5) (TIM1.7) (TIM2.6) (TIM2.4) (TIM2.7) (TIM2.6) (TIM2.6) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.5) (TIM1.5) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 TIM1.2 TIM1.1 TIM1.0 (TIM1.5) (TIM1.4) (TIM2.6) (TIM2.4) TIM2.7 TIM2.0 BH R/W 0000 TIM2.3 TIM2.2 (TIM2.5) (TIM2.5) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.5) TIM1.1 TIM1.0 TIM1.7—TIM1.0: 8 bit TIMER 1 counter value, read of write must follow fixed sequence as shown below:  (1) Write: write low nibble first, and the read high nibble.  TIM2.0 OBH R/W 0000 TIM2.3 (TIM2.7) (TIM2.6) (TIM2.5) (TIM2.4) (TIM2.4) (TIM2.7) (TIM2.6) (TIM2.5) (TIM2.4) (TIM2.7) (TIM2.6) (TIM2.4) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.4) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.4) (TIM2.7) (TIM2.7 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.2) (TIM1.5) (TIM2.5) (TIM2.7) (TIM2 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.7) (TIM1.6) (TIM1.5) (TIM2.6) (TIM2.7) (TIM2.5) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.5) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.8) (TIM2.7) (TIM2.8) (TIM2.7) (TIM2.8) (TIM2.7) (TIM2.8) (TIM2.9) (TIM2.7) (TIM2.9) (TIM2.7) (TIM2.8) (TIM2.9) (TIM2.7) (TIM2.9) (TIM2.7) (TIM2.8) (TIM2.7) (TIM2.8) (TIM2.7) (TIM2.8) (TIM2 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.6) (TIM1.5) TIM2.2 (TIM2.7) (TIM2.6) (TIM2.5) TIM2.0 OBH R/W 0000 TIM2.3 (TIM2.7) (TIM2.6) (TIM2.5) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.7) (TIM2.6) (TIM2.7) (TIM2.7 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TiM1.3 (TiM1.6) (TiM1.5) (TiM1.4) (TiM1.5) (TiM2.6) (TiM2.7) (TiM2.7) (TiM2.6) (TiM2.5) (TiM2.4) (TiM2.7) (TiM2.6) (TiM2.5) (TiM2.4) (TiM2.7) (TiM2.6) (TiM2.5) (TiM2.4) (TiM2.7) (TiM2.6) (TiM2.5) (TiM2.4) (TiM2.7) (TiM2.6) (TiM2.5) (TiM2.7) (TiM2.6) (TiM2.7) (TiM2.7) (TiM2.6) (TiM2.7) (TiM2 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.6) TIM1.5 (TIM1.5) TIM1.4 (TIM1.5) TIM1.7 -TIM1.0 8 bit TIMER 1 counter value, read or write must follow fixed sequence as shown below:  (1) Write: write low nibble first, and the write high nibble.  (2) Read: read low nibble first, and the write high nibble.  (3) Read: read low nibble first, and the write high nibble.  (4) R/W 0000 TIM2.3 (TIM2.2 (TIM2.5) (TIM2.5) (TIM2.4) (TIM2.4) (TIM2.4) (TIM2.4) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.7-TIM2.0: 8 bit TIMER 2 counter value, read or write must follow fixed sequence as shown below:  (1) Write: write low nibble first, and the write high nibble.  (2) Read: read low nibble first, and the write high nibble.  (2) Read: read low nibble first, and the read high nibble.  (3) Read: read low nibble first, and the write high nibble.  (4) Read: read low nibble first, and the read high nibble.  (5) Read: read low nibble first, and the read high nibble.  (6) Read: read low nibble first, and the read high nibble.  (7) Read: read low nibble first, and the read high nibble.  (8) Read: read low nibble first, and the read high nibble.  (9) Read: read low nibble first, and the read high nibble.  (1) Write: write low nibble first, and the read high nibble.  (1) Read: read low nibble first, and the read high nibble.  (2) Read: read low nibble first, and the read high nibble.  (3) Read: read low nibble first, and the read high nibble.  (6) Read: read low nibble first, and the read high nibble.  (7) Read: read low nibble first, and the read high nibble.  (8) Read: read low nibble first, and the read high nibble.  (9) Read: read low nibble first, and the read high nibble.  (1) Write: write low nibble first, and the read high nibble.  (1) Write: write low nibble first, and the read high nibble.  (2) Read: read low nibble first, and the read high nibble.  (3) Read: read low nibble first, and the read high nibble.  (4) Read: read low nibble first, and the read high nibble.  (5) Read: read low nibble first, and the read high nib |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.5) (TIM1.5) (TIM1.5) (TIM1.6) (TIM1.5) (TIM1.5) (TIM2.6) (TIM2.7) (TIM2 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.7) TIM1.2 (TIM1.6) (TIM1.5) (TIM1.4) TIM1.7~TIM1.0: 8 bit TIMER 1 counter value, read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble.  TIM2 OBH R/W 0000 TIM2.3 (TIM2.7) (TIM2.6) (TIM2.5) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.6) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.6) (TIM2.6 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.6) (TIM1.5) TIM1.0 (TIM1.4) (TIM1.6) (TIM1.5) (TIM1.4) (TIM1.6) (TIM1.5) (TIM1.4) (TIM1.6) (TIM1.6 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.6) (TIM1.5) (TIM1.4) (TIM1.4) (TIM1.5) (TIM1.4) (TIM1.5) (TIM1.4) (TIM1.4) (TIM1.5) (TIM1.4) (TIM1.4) (TIM1.5) (TIM1.4) (TIM1 |         |       |       |      |             |            |            |             |                                         |

| TIM1 OAH R/W 0000 TIM1.3 (TIM1.6) (TIM1.5) (TIM1.4) (TIM1.5) (TIM1.6) (TIM1.4) (TIM1.6) (TIM1.5) (TIM1.7-TIM1.0: 8 bit TIMER 1 counter value, read or write must follow fixed sequence as shown below:  (1) Write: write low nibble first, and the write high nibble.  (2) Read: read low nibble first, and the read high nibble.  TIM2 OBH R/W 0000 TIM2.3 (TIM2.6) (TIM2.5) (TIM2.5) (TIM2.4) (TIM2.4) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.4) (TIM2.5) (TIM2.4) (TIM2.6) (TIM2. |         |       |       |      |             |            |            |             |                                         |

| TIM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |       |       |      |             |            |            |             |                                         |

| TIM2  OBH  R/W  O000  TIM2.3 (TIM2.7) (TIM2.6)  TIM2.1 (TIM2.5)  TIM2.1 (TIM2.5)  TIM2.2 (TIM2.6)  TIM2.3 (TIM2.7) (TIM2.6)  TIM2.1 (TIM2.6)  TIM2.4  TIM2.4  TIM2.5  TIM2.7  TIM2.7  TIM2.0 (TIM2.4)  TIM2.7  TIM2.7  TIM2.0 (TIM2.4)  TIM2.7  TIM2.7  TIM2.0: TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.7  TIM2.7  TIM2.7  TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.1 (TIM2.4)  TIM2.7  TIM2.1 (TIM2.4)  TIM2.2  TIM2.1 (TIM2.4)  TIM2.2  TIM2.1 (TIM2.4)  TIM2.2  TIM2.1 (TIM2.4)  TIM2.2  TIM2.1 (TIM2.5)  TIM2.2  TIM2.1 (TIM2.4)  TIM2.0  TIM2.7  TIM2.0  TIM2.0  TIM2.7  TIM2.0  TIM2.0  TIM2.7  TIM2 | TIMA    | 0.411 | D/M   | 0000 | TIMA O      | TIMA O     | TIMA A     | TIMA O      |                                         |

| Sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read low nibble first, and the read high nibble. (2) Read: read low nibble first, and the read high nibble. (3) Read: read low nibble first, and the read high nibble. (4) Write: write low nibble first, and the write high nibble. (5) Read: read or write must follow fixed sequence as shown below: (6) Write: write low nibble first, and the write high nibble. (7) Read: read low nibble first, and the read high nibble. (8) Read: read low nibble first, and the read high nibble. (9) Read: read low nibble first, and the read high nibble. (1) Write: write low nibble first, and the read high nibble. (1) Write: write low nibble first, and the read high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read or write nust follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2 | TIIVIT  | UAH   | R/VV  | 0000 |             |            |            |             |                                         |

| TIM2  OBH  R/W  O000  TIM2.3 (TIM2.7) (TIM2.6)  TIM2.5  TIM2.0 (TIM2.5)  TIM2.0 (TIM2.4) (TIM2.5)  TIM2.0 (TIM2.4) (TIM2.5)  TIM2.0 (TIM2.4) (TIM2.6)  TIM2.0 (TIM2.4) (TIM2.6)  TIM2.0 (TIM2.4) (TIM2.6)  TIM2.0 (TIM2.7~TIM2.0: 8 bit TIMER 2 counter value, read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read low nibble first, and the write high nibble. (2) Read: read low nibble first, and the read high nibble.  IOC_PD  OCH  R/W  O000  IOCD3  IOCD2  IOCD1  IOCD0  Port D input/output direction select 1: set port as output port individually 0: set port as input port individually 0: set port as input port individually 0: set port as input port individually write data to PD0~PD3 (I/O direction is defined by IOC_PD register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |       |       |      | (111111111) | (111111.0) | (111111.0) | (1 IIVI 11) |                                         |

| TIM2  OBH  R/W  O000  TIM2.3 (TIM2.7)  TIM2.2 (TIM2.6)  TIM2.5  TIM2.1 (TIM2.5)  TIM2.0 (TIM2.4)  TIM2.0 (TIM2.4)  TIM2.7~TIM2.0: 8 bit TIMER 2 counter value, read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble.  (2) Read: read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble.  (2) Read: read low nibble first, and the read high nibble.  (2) Read: read low nibble first, and the write high nibble.  (3) Read: read low nibble first, and the write high nibble.  (4) Port D input/output direction select 1: set port as output port individually 0: set port as input port individually 0: set port as input port individually write data to PD0~PD3 (I/O direction is defined by IOC_PD register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |       |       |      |             |            |            |             |                                         |

| TIM2  OBH  R/W  O000  TIM2.3 (TIM2.7)  TIM2.5  TIM2.1 (TIM2.5)  TIM2.4  TIM2.7~TIM2.0: 8 bit TIMER 2 counter value, read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble. (2) Read: read low nibble first, and the write high nibble. (2) Read: read low nibble first, and the write high nibble.  IOC_PD  OCH  R/W  O000  IOCD3  IOCD2  IOCD1  IOCD0  Port D input/output direction select 1: set port as output port individually 0: set port as input port individually 0: set port as input port individually  DATA_PD  ODH  R/W  XXXX  DPD3  DPD1  DPD0  Read port D data from PD0~PD3 port of write data to PD0~PD3 (I/O direction is defined by IOC_PD register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |       |       |      |             |            |            |             |                                         |

| TIM2  OBH  R/W  O000  TIM2.3 (TIM2.7)  TIM2.2 (TIM2.6)  TIM2.5  TIM2.1 (TIM2.5)  TIM2.4  TIM2.0 (TIM2.4)  TIM2.7~TIM2.0: 8 bit TIMER 2 counter value, read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble.  (2) Read: read low nibble first, and the read high nibble.  TIM2.7~TIM2.0: 8 bit TIMER 2 counter value, read or write must follow fixed sequence as shown below: (1) Write: write low nibble first, and the write high nibble.  Port D input/output direction select 1: set port as output port individually 0: set port as input port individually 0: set port as input port individually  DATA_PD  ODH  R/W  XXXX  DPD3  DPD1  DPD0  Read port D data from PD0~PD3 port of write data to PD0~PD3 (I/O direction is defined by IOC_PD register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |       |       |      |             |            |            |             |                                         |