——作者:Terry Yuan 公司:骏龙科技

在上篇《ADI音频在PCBA里的通用传输格式》里,我们介绍了通用音频在 PCBA 中的传输格式,其中涉及到多种格式,本文将挑选一个最常用的数字传输格式进行相关分析,以帮助大家了解如何合理地在软硬件上进行设计。

在 PCB 板内的音频设计时,很多时候都是以模拟信号作为前后输入输出,但是板内更多是以数字信号为主,例如我们可以看到各种 aux、同轴、莲花口等信号输入。只要音频需要进行处理,一般都是需要转成数字信号来进行的,比如当我们在用 FPGA、DSP、单片机等系统时。大多数情况下,简单 2 通道的实现在软硬件上还是比较简单,但是上升到 TDM8 以上,很多客户就会面临稳定性的问题。接下来将分两个板块——软件和硬件,为大家说明如何有效规避这些风险。

TDM 在软件配置上的注意项

上文有说到 TDM 协议一般是三根线 (MCLK 除外),有的编解码会有四根线,主时钟线束一般是恒定输入的,另外三根是 BCLK、SYNC、以及 SDATA (DATA 一般会有 DTX、DRX,或者自己灵活配置为 DTX 或 DRX)。那发射端和接收端要如何配置才能匹配起来呢?下面将进行一一介绍:

♦ 确定传输多少通道的音频

我们需要根据传输多少通道的音频来选择 TDM 接口,一般是 TDM2/4/8/12/16/32 这几种,具体需要根据实际情况来选择。然后确定采样率、位深,以此得到确切的位时钟数据。例如 TDM16,采用 48khz 的采样率以及 32bit 的位深,那么其确定的 BCLK 频率就是 16 * 48khz * 32bit = 24.576Mhz。在驱动中一般需要配置具体 TDM 类型、位深和采样率,这里的配置,发射端和接收端需要保持一致。

♦ 确定 SYNC 的类型和极性

对于帧同步信号,它的频率一般就是采样频率,比如 TDM16 的格式,在帧同步信号的一个周期内,可以传输 16 个通道的数据。同时,它有脉冲模式和 50/50 占空比模式。脉冲模式是以第一个位时钟增加一个脉冲开始,到该周期结束。50/50 占空比模式,是高低电平分别占用一半的通道,具体请查看 datasheet 的示例图。它还有一个极性,即上升沿触发还是下降沿触发。这一部分发射端和接收端也需要保持一致。

♦ 确定 BCLK 的极性

在第一点我们已经确定了 BCLK 的时钟大概是多少,接下来还需要进行下一步的极性配置。这个极性配置其实是对应于 SDATA 位来说的,而且需要区分驱动沿和采样沿,一般情况下,发射端的驱动沿配置要和采样沿相反,有的格式要相同,具体要核对数据手册上对于该内容的描述。

其实就算配置的不对,也会有声音输出。基本上有经验的工程师都能够听出来,或者通过对数据数组中的数据进行分析,不对应的边沿,采集下来的数据无非就是溢出,或者少了一位。当发现 1khz 的正弦波进去,采出的数据具备这种波形特点,但是高位没数据,或者低位没数据,听起来原声小,噪声大,实际上就是这个原因造成的。另外,这个配置发射端和接收端可能相反,也可能相同,因此需要进行比对。

♦ 确定 SDATA 位的格式

这里说的格式和数据传输中 MSB 以及 LSB 息息相关,这一点是针对于 SYNC 来的。在 SYNC 的周期开始时,我们可以选择 delay 1 或者左对齐右对齐等格式。这里是要严格对齐的,不然数据肯定是采集不正确的,该配置发射端和接收端需要保持一致。

以上基本就是 TDM 在软件配置中的一些注意点,当然可能有一些芯片在这些配置的基础上增加了某些其他功能,这需要具体查看对应的 datasheet。比如 ADAU1452 添加了 flexTDM 功能,AD2428 的 TDM 增加了 delay 1 SYNC 以及 offset 等等,这样做的目的基本上都是为了提升该芯片 IP 的兼容性。有一些做得差的厂商,可能他们的 IP 都无法支持 TDM32,只能支持到 TDM8,但总体来说,以上的配置指导说明能够涵盖这些基础配置。

TDM 在硬件设计上的注意项

很多人会说 TDM 不就是几根线连起来就可以了吗?然后 IIS 跑起来也没出过问题啊?大部分客户可能很少设计过 TDM8 以上的信号,同时极端情况出现的比较少,这是因为消费电子的音频受扰环境少,但在汽车电子中,外界环境比较复杂,时常出现一些不稳定的现象,下文将集中描述一些问题,同时给大家提供一些解决思路。

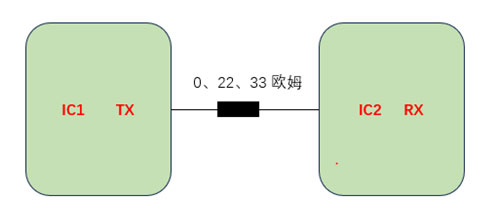

为什么要在发射端和接收端加电阻?

如下图 (图1) 所示,我们常常在 IC1 和 IC2 中间加个电阻,很多工程师其实都不清楚为什么要加它,它到底加多大?以下为大家进行详细说明:

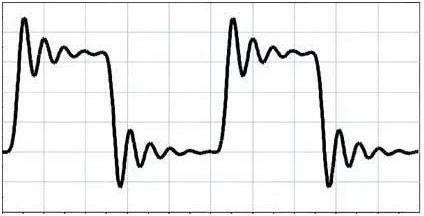

在芯片的 TDM IP 接口设计时,实际上发射端的阻抗一般都是偏低的,大概在 17-40Ω 左右,PCB 的单端走线一般是 50Ω,而接收端的阻抗通常又比较大,这就是一个典型的不连续不匹配的系统,所以我们通常需要加一个 22Ω 的电阻,加到靠近的发射端,这样基本能在整体上保持阻抗的连续问题。不匹配典型的波形就是过冲和振铃,如下图 (图2) 所示,而这种问题的风险就是容易导致接收端误解码。

总的来说,信号线上的电阻主要是为了匹配阻抗,降低噪声,而限流和保护作用基本上涉及比较少,因为功率总体上比较小。

在发射端和接收端到底要不要加旁路或者去耦电容?

接下来通过一个真实的案例加以说明。某客户已经把功放的所有产品需求设计好了,并且进入量产了,但是将产品装到车上后,在低温或者一些比较极限的情况下,突发无声等情况。经过许久排查,发现核心问题还是产生在 TDM 的旁路电容上。

为什么要加该电容?在汽车电子的产品中,我们都要过车规认证,这时候会产生让非常多工程师头疼的问题:当 EMI 和 EMC 等级要求过高而无法通过时,工程师就会考虑加一些电容了。一方面因为是旁路或者去耦接地能够吃掉相当一部分的能量,使得辐射减少。另一方面还能够降低噪声,提高电磁兼容性。

另外,在实际应用中还得注意谐振频率的问题,尤其是和信号频率接近的谐振频率。产生谐振后,最容易出现在我们信号的阈值附件波形抖动,尤其在一些极端条件下,电容器的温漂属性,配合自身的 ESR,以及电路中的电阻构成 RC 滤波电路。如果出现了这个问题,基本是由于 TDM 信号判定不了或者错位导致的。所以在这个电容器上,不需要经过严苛认证的一般不必加,需要过认证的要适量加大容量或者减小容量,尤其是上升沿下降沿出现回勾,而且这个频率一般是很难计算的,它和发射接收、走线以及电容本身的 ESR 都有关系。

总之,在添加电容、电阻的时候也需要用心,因为如果这些条件没添加好,都会影响波形质量。电阻加得大,波形变成三角波,电容加得大,波形爬坡变成一条弧线,上升下降沿的时间都大大增加了,从而进一步影响波形质量。

综上所述,只要对以上介绍的两点内容和硬件的 layout 设计稍作注意,一般都可以设计出比较稳定的产品。有一些客户出问题少,是因为大部分的 IIS 带宽足够低,很少出现这种情况,同时容错率比较高,芯片厂商设计的 IP 足够覆盖。这侧面也反应出,在设计中,如果使用 TDM8 足够,就不需要使用 TDM16 或者 32,因为会增加一些不必要的风险。

总结

根据上面的介绍,相信大家对 TDM 的协议和设计方式已经了解,这个格式差不多算是通用音频的基石,用的非常多,希望能对大家的设计有所帮助。同时大家在选择上可以尽可能选择支持 TDM16、32 的这种芯片,因为一般这种芯片的 IP 设计的带宽都要比那些只支持不到 TDM8 的芯片要好,尤其体现在一些高算力的 SOC 或者 DSP 上。

免责声明: 本文章转自其它平台,并不代表本站观点及立场。若有侵权或异议,请联系我们删除。谢谢! Disclaimer: This article is reproduced from other platforms and does not represent the views or positions of this website. If there is any infringement or objection, please contact us to delete it. thank you! |

- 上一篇:霍尔传感器的检测

- 下一篇:LED数码显示管的结构